Asian IBIS Summit Tokyo, JAPAN November 17, 2017

## On die De-cap Modeling Proposal

Murata Kazuki (RICOH COMPANY, LTD.)

JEITA

Semiconductor & System Design Technical Committee LPB Interoperable Design Sub-Committee Modeling Working Group

## Introduction

- Digital IF

- Data rate enters the GHz range.

- Supply voltage further declined.

- -> SI&PI&EMI Analysis became much more important.

- Added Keywords in IBIS Version 5.0

- [Composite Current]:Consumption current IT-Waveform.

- [ISSO PU(PD)]:Characteristic between supply voltage and PU.

- -> IBIS is now useful for Chip PDN-aware SI&PI&EMI analysis.

# Chip PDN characteristic

- However, Almost all IBIS models don't have Chip PDN characteristic.

- On die Resistance affects IR-Drop and Q factor.

- On die De-cap affects High frequency power-supply noise.

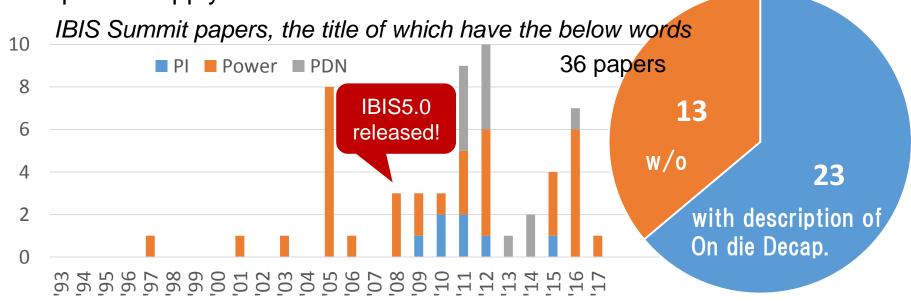

Many papers reported in IBIS Summit describe importance of On die De-cap, because it is one of the few solution that reduce high frequency power-supply noise.

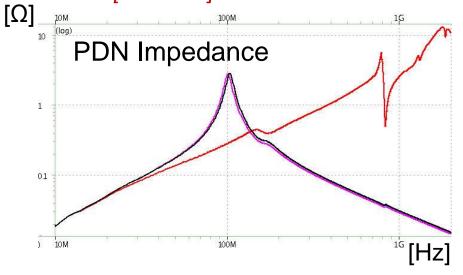

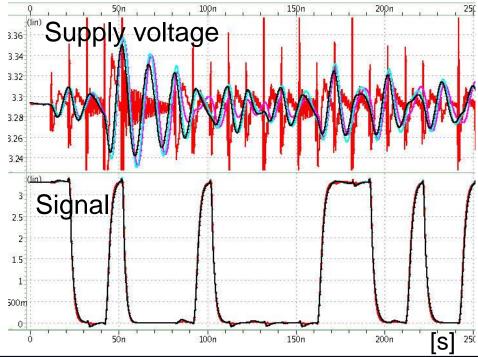

## On die De-cap impact

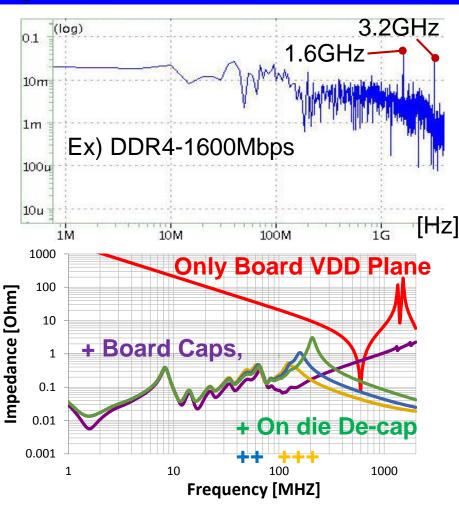

The frequency spectrum of high speed digital IF consumption current depends on its data rate.

To reduce impedance of high frequency range makes supply-voltage quality better.

-> Only On die De-cap can affect supply voltage quality in high frequency range.

# A Survey of On die De-cap model

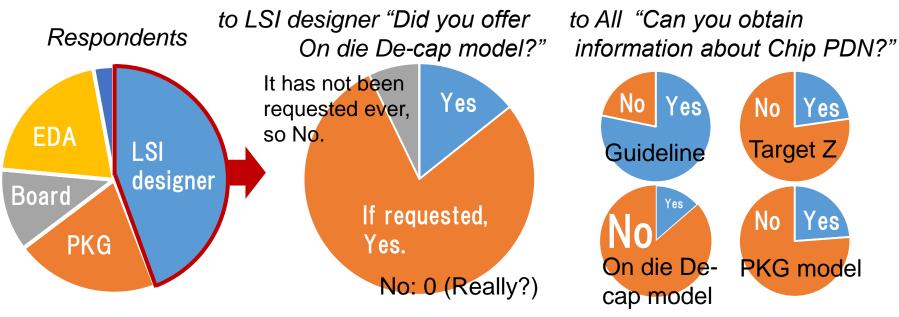

But, board and system designers can hardly obtainOn die De-cap model.

A Survey by JEITA LPB-SC MDL-WG @LPB developpers workshop 2017.9.2

- In some cases LSI designers offer On die De-cap model on request. And they wonder "Which model format is suitable for our customer?"

- -> It's time to add new IBIS keywords about On die De-cap!

# On die De-cap model in IBIS

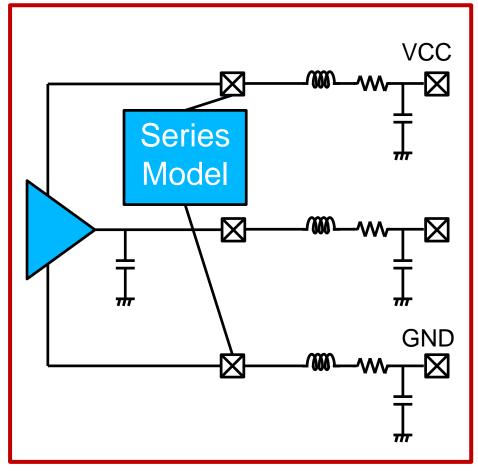

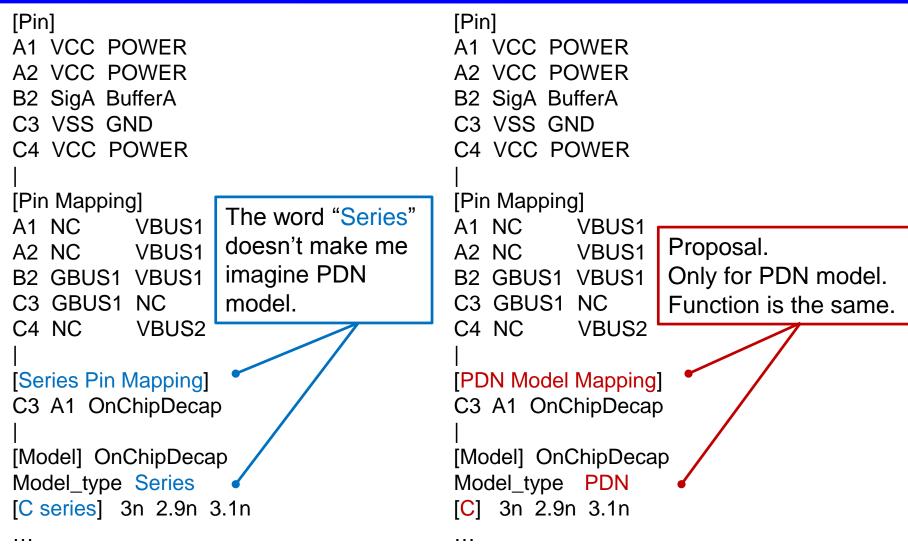

[Model] Model\_Type Series [Pin] (Pkg) Ccomp Series Model Ccomp

'Modeling the On-die De-cap of IBIS5.0 PDN-aware Buffers' Lance Wang, and Randy Wolff Nov 2011

# On die De-cap model format proposal

### Another method

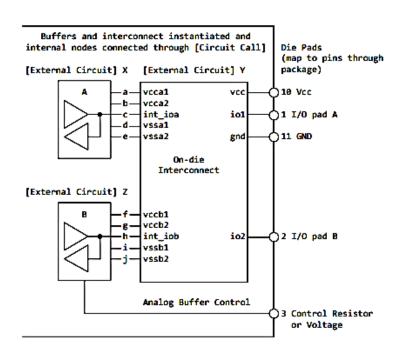

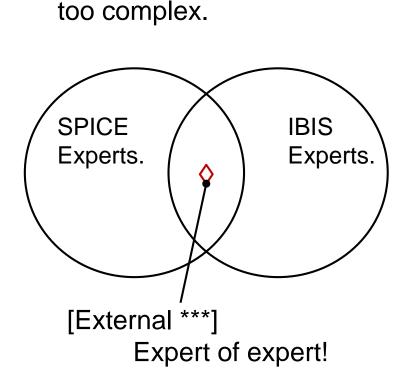

■ [External Model] or [External Circuit] can reference other files which are written using the SPICE or IBIS-ISS.

Figure 21 - Example Showing [External Circuit] Ports

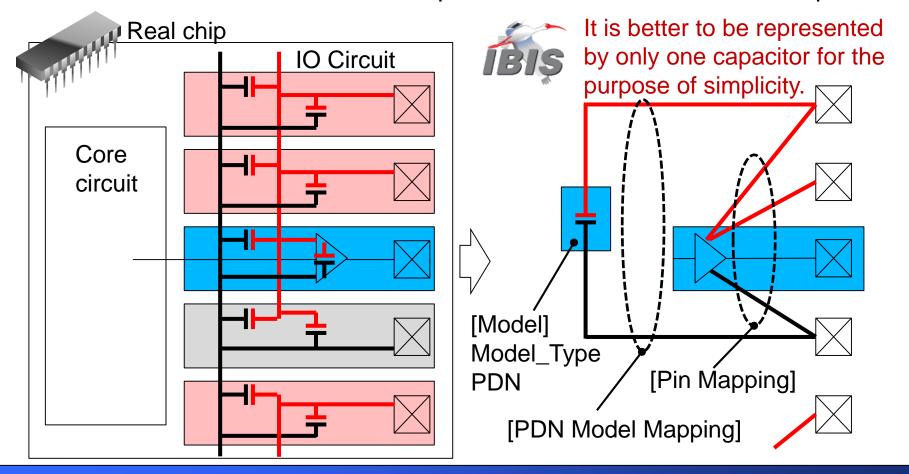

# On die De-cap model and real circuit

There are De-cap cell, parasitic capacitance between VCC metal and GND metal, and MOS capacitance in IO circuit of real chip.

# Topology of On die De-cap model

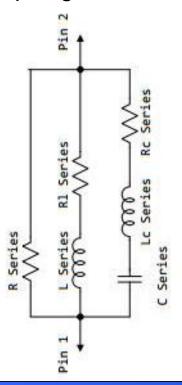

■ Model\_Type Series

IBIS maker can choose which element to enable. There are 30 circuit topologies.

Proposal: Model\_Type PDN

Only one topology available. (T.B.D.)

## Modeling On die De-cap

- I hope that chip vendor can easily provide On die De-cap model by this proposal.

- However, even if this proposal is adopted, it takes some time to spread this model.

"I want to know this chip's PDN model right now!" -> Try measuring.

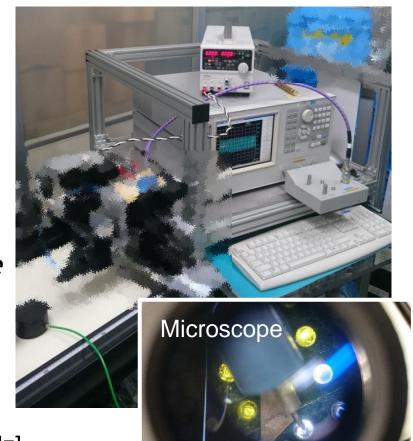

# Measuring On die De-cap model

#### Method

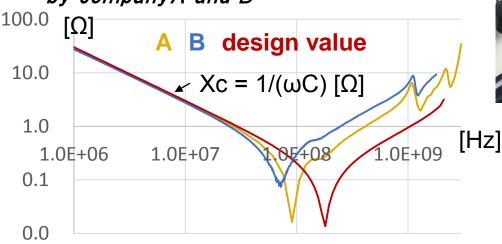

We measured impedance between VCC pin and GND pin by Impedance analyzer (or Network analyzer). Supply voltage was applied these pins also.

#### Result

Measurement result of company A's ASIC by company A and B

## Correlation

■ Provisional On die De-cap model : One capacitor. +

[Series Pin Mapping]

C3 A1 OnChipDecap

[Model] OnChipDecap

Model\_type Series

[C series] XXX

1 Measurement: 5.55nF

2Design value:5.25nF

3 Without De-cap:0nF

**4**SPICE IO model + Design value: 5.25nF

### JEITA LPB-SC MDL-WG

LPB Sub-Committee Modeling working group

We have been studying SI, PI, EMI, and Thermal simulation model problems for proposing new models to solve them and promoting standardization.

- Contents of activities in 2017

- Survey of On die De-cap model availability

- Standardization of On die De-cap measuring method

- Proposal of measured On die De-cap model's circuit topology

- Proposal of IBIS On die De-cap model

## 10<sup>th</sup> LPB Forum

#### ■ "LPB"

stands for LSI & Package & Board. When new products are produced or for creating competitive products, plan, design, production for LPB went closely coordinated to each other, and we are working hard to aim for win-win.

### "LPB Forum"

- Introduces case examples of Interoperable design

- 9<sup>th</sup> LPB Forum's papers.

LPB format overview

A case example of conceptual design with LPB format

IBIS-LPB design kit

PI analysis with LPB format and IBIS5.0

• 10<sup>th</sup> LPB Forum date:2018.3.9 Fri.

### Conclusion

It has long been known that the chip's characteristics have a large influence on the whole PDN.

However, chip PDN model still is not widespread. Therefore, We proposed to add explicit keywords of chip PDN to IBIS.

We confirmed that these keywords improve SI "Power Aware" simulation. And we introduced On die De-cap measuring method.

After we will study modeling from measurement, We will propose concrete circuit.

Thank you!