## JEITA LPB-SC

- ・フロントローディング TG

- ・LPBライブラリ整備 TG

Annual Report 2020年度

# フロントローディング TG

### ■フロントローディング TG

『活動の目的』 モデルベース設計手法により、各設計工程のモデル粒度で実現可能 なことを定義する。

『具体的取組』 モチーフを決定。 今期はEMCをターゲットに、各設計工程で期待されるアウトプット、それに対し必要な情報を議論する。 具体的にはシステムをCフォーマットで定義し、対象ICに対し IEC62433をLPB-Cフォーマットにラッピングした場合の可能性を 議論する。

『2020年度成果物』 IEC62433を活用する場合の設計フローを定義する 『日程』

|           | 5月 | 6月              | 7月       | 8月             | 9月              | 10月              | 11月              | 12月          | 1月    | 2月             | 3月                             |

|-----------|----|-----------------|----------|----------------|-----------------|------------------|------------------|--------------|-------|----------------|--------------------------------|

| LPB-SC    |    | <b>▲</b> (6/19) |          |                |                 | <b>▲</b> (10/23) |                  |              |       | <b>▲</b> (1/8) | <b>▲</b> (3/5)                 |

| インフラ-TG@タ | 東芝 | <b>▲</b> (6     | /5)      | <b>▲</b> (8/7) | <b>▲</b> (8/28) |                  | <b>▲</b> (10/16) | <b>▲</b> (12 | (/11) |                | <b>▲</b> (2/12) <b>▲</b> (4/9) |

| イベント      |    |                 |          |                | • •             | /11-12)          |                  | <b>A</b>     |       | <b>A</b>       | <b>▲</b> (3/5)                 |

| 1 131     |    |                 |          |                |                 | 宿                |                  | JE'          | VeC?  | Design         | LPBフォーラ                        |

|           |    | IEC62433        | 3をLPBフォ・ | ーマットに          | ▲1次             | 7成果報告            |                  |              |       | CON?           | ▲1次成果報告                        |

|           |    | ラッピングしたケースを作成。  |          |                | ,               | ー ・              |                  |              | るEMC核 | -              |                                |

## 概要

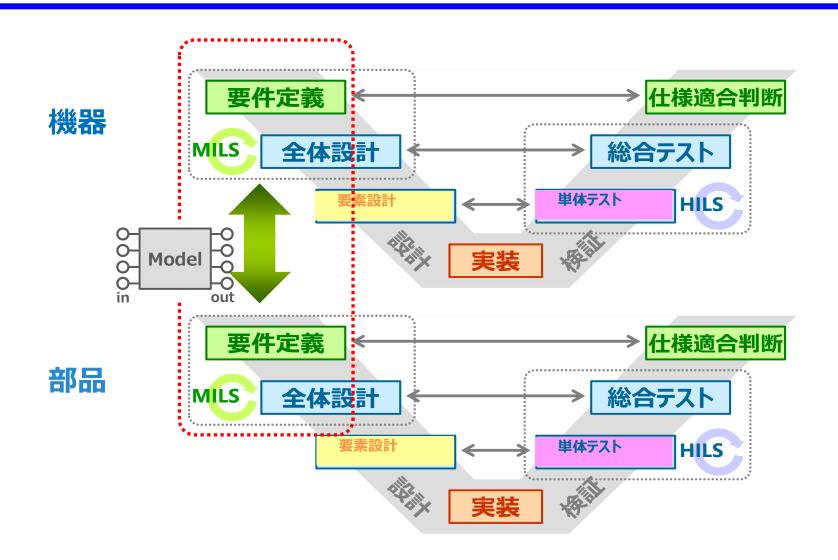

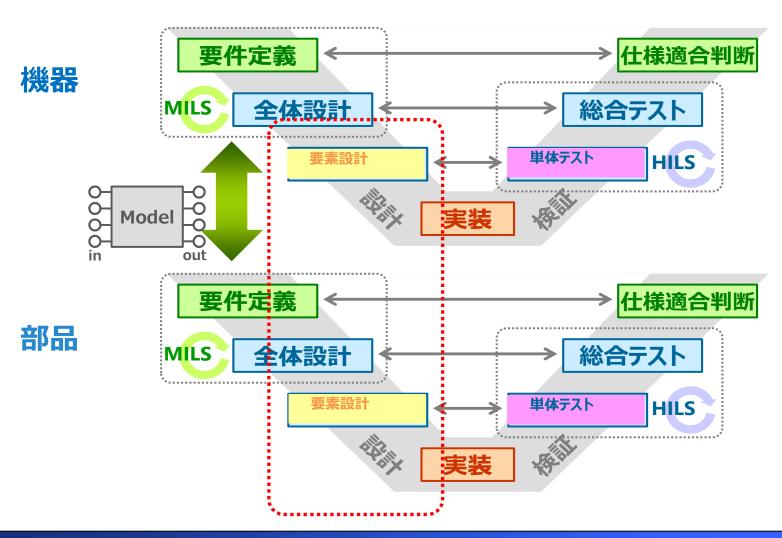

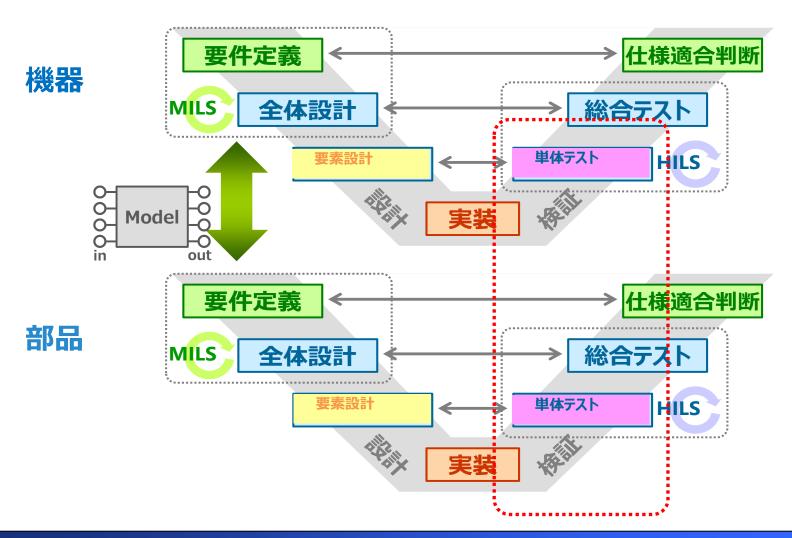

これまでLSI-Package-PCBのHWの部分にフォーカスして取り組み、フォーマットの 策定を始め、LPB協調設計のメソドロジーに関する枠組みを作ってきた。

これらのLPB協調設計が、HW-SW連携や、モデルベース開発を主とした システム設計の中に置かれた場合に、どういった設計プロセスになるのか、そのためには 現在のLPBフォーマットで問題ないのか、問題ある場合、どういったフォーマットである べきなのかの議論を行ない、各設計工程のモデル粒度で実現可能なことを定義する。

# 20年度の方針

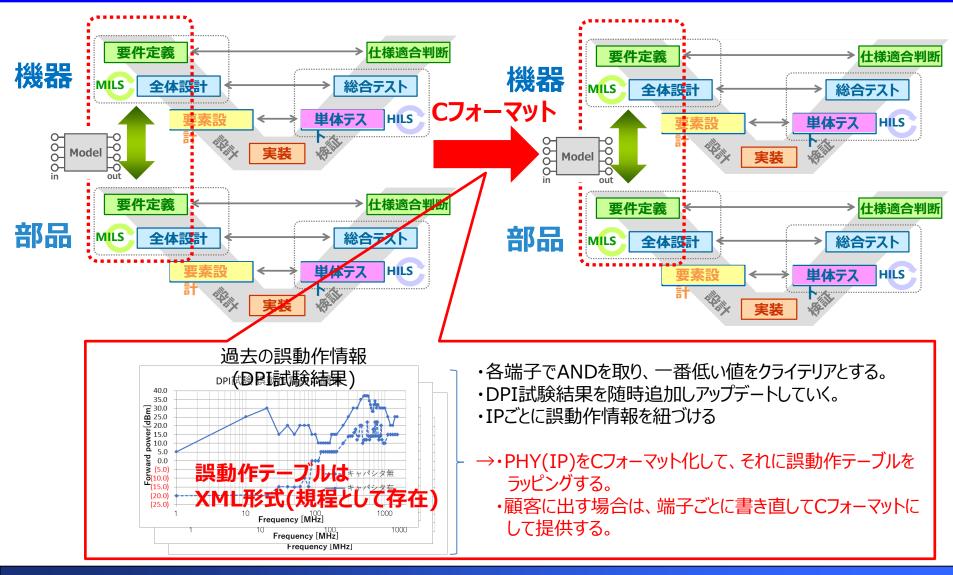

20年度はバウンダリーTGが19年度に検討したIEC62433(DPI)の結果を、実際の設計フローに組み込んだ場合にどうあるべきかを定義する。

## 方法

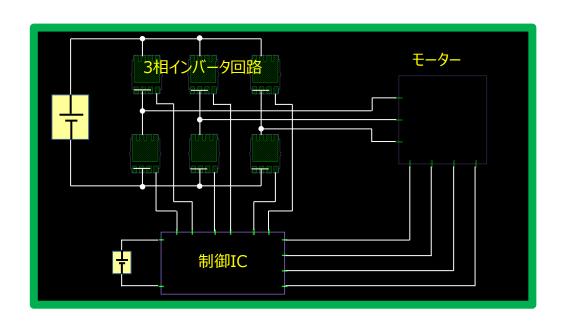

HW-SW連携や、モデルベース開発を主としたシステム設計をはじめから議論すると 抽象度が高いため、システムとして一般的な3相インバータ回路をモチーフとし、 EMCをターゲットに、各設計工程で期待されるアウトプット、それに対し必要な情報を 議論する。

具体的には3相インバータ回路を設計すると仮定した場合の各設計工程での回路をCフォーマットで表現し、対象部品に対しIEC62433をLPB-Cフォーマットにラッピングした場合の可能性を議論する。

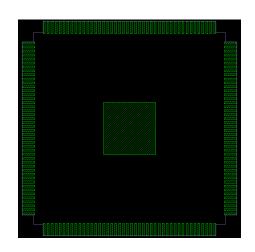

3相インバータをモチーフに、このフェーズでLPB-Cフォーマットを使い部品配置をした結果が以下の通り。

#### 課題は

- ・汎用部品は現在のLPB-Cで問題ないがカスタム部品は形状がまだ存在しなかったり端子数も確定していない場合が多い

- ・機器側からの要求をモデルで表現するためには、何らかの箱を用意する必要がある であることが分かった。

この場合、まだ確定していない部品はシンボルで定義し、そのシンボルの中に動作モデルを記述する必要がある。ただ現在のLPB-Cフォーマットはシンボルを記述することができずBOXで表現するしかない。

またネット記述に関しても、現在Nフォーマットがあるがこれは端子間の定義であり、回路記述には対応できていない。

もしこれらを表現可能になると、論理検証と物理検証の中間のようなものを表現することでHW検証を可能とすることができるとの結論に達した。

なお、このフェーズで可能なHW検証とは以下を想定している。

- ・簡易熱シミュレーション

- ・簡易波形シミュレーション

ここでの次期フォーマットへの要望は以下である。

- 「要望① シンボルをLPBフォーマットで記述可能とする。」

- 「要望② システム構成図(回路図)をLPBフォーマットで記述可能とする。」

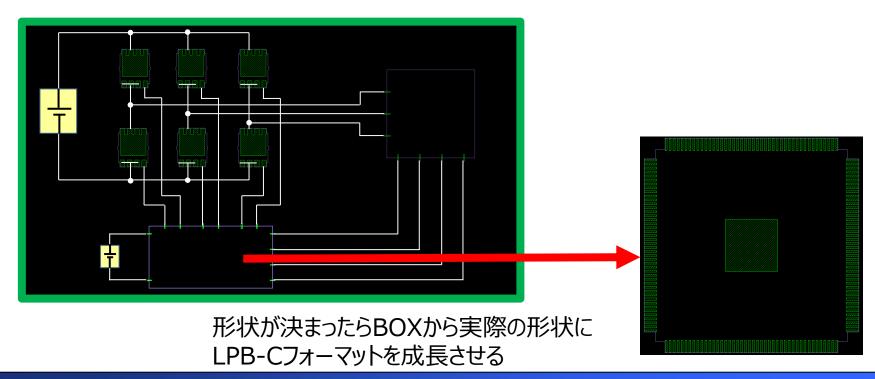

このフェーズになると、部品形状も決まってくるので、ボックスから実際の部品形状に LPB-Cフォーマットを置き換える必要がある。

課題は、現在のLPB-Cフォーマットではモデルを置き換えなければならないことである。 ここでの次期フォーマットへの要望は以下である。

「要望③ シンボルからセルに成長させ、形状もラッピング可能とする。」

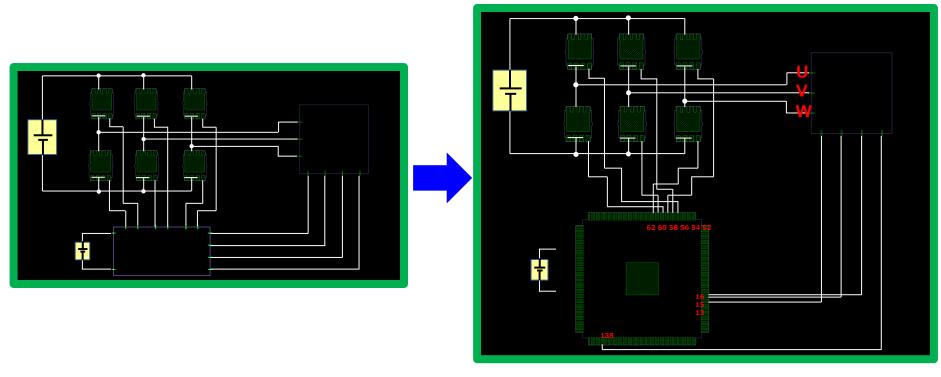

### 以下が部品をBOXから、詳細な形状に置き換えた結果である。

なお、このフェーズで可能なHW検証とは以下を想定している。

- ・やや詳細な熱シミュレーション

- ・やや詳細な波形シミュレーション

- ・簡易電源ノイズシミュレーション

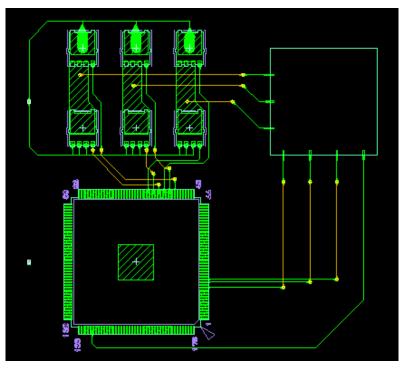

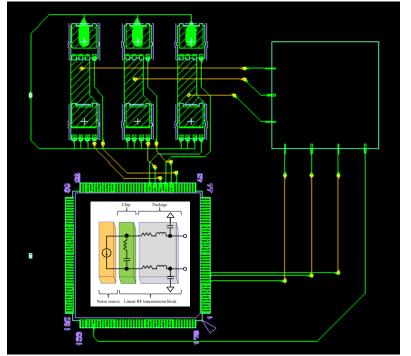

#### 更に、詳細にレイアウト配線をした結果が以下である。

なお、このフェーズで可能なHW検証は以下を想定している。

- 詳細な熱シミュレーション

- ・詳細な波形シミュレーション

- ・やや詳細な電源ノイズシミュレーション

- ・簡易EMCシミュレーション

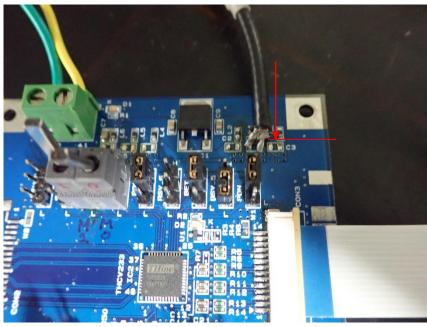

このフェーズになると、実測による半導体モデルが出来てくる。

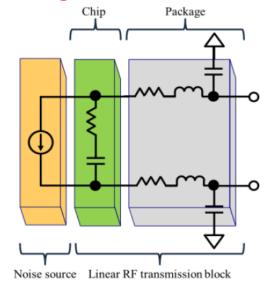

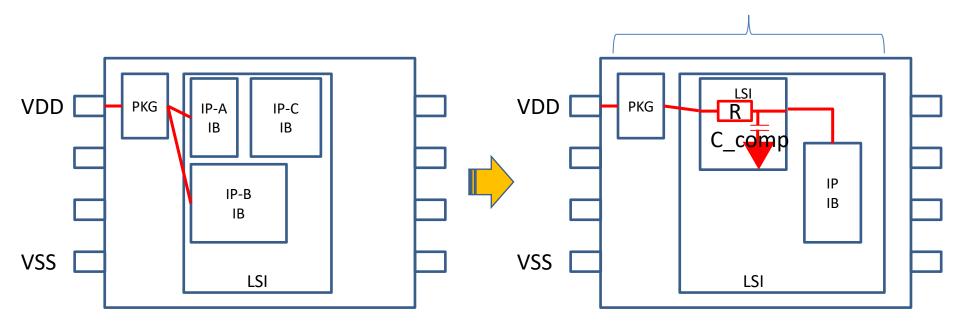

現在、IEC 62433バウンダリモデルTGがEMCモデル(ESD含む)を進めており、このモデルをLPB-Cフォーマットに取り込むことになる。

その際、動特性(IA)に関しては、動作シナリオや組み合わせ、カップリング(IBC)によって特性が変わるため、静特性(PDN)と動特性(IA)を分けて、IAをシナリオごとに表現する必要がある。課題は、現在のLPB-Cフォーマットではその辺りが表現できないことである。ここでの次期フォーマットへの要望は以下である。

「要望④ PDNとIAを分け、IAのモデルを複数持たせられることを可能とする。」

各ピンにEMCモデルを 割り当てる

最終的には、以下のようにチップ内に半導体モデルが付加されて、詳細なSimが可能と

なる。

今後、IEC 62433バウンダリモデルTGと 融合を図り、システム全体の検証を達成 していく。

なお、このフェーズで可能なHW検証とは以下を想定している。

- ・詳細な熱シミュレーション

- ・詳細な波形シミュレーション

- 詳細な電源ノイズシミュレーション

- ・詳細なEMCシミュレーション

### における検証

### ケース1. 全く新規のLSI設計の場合

Page 15

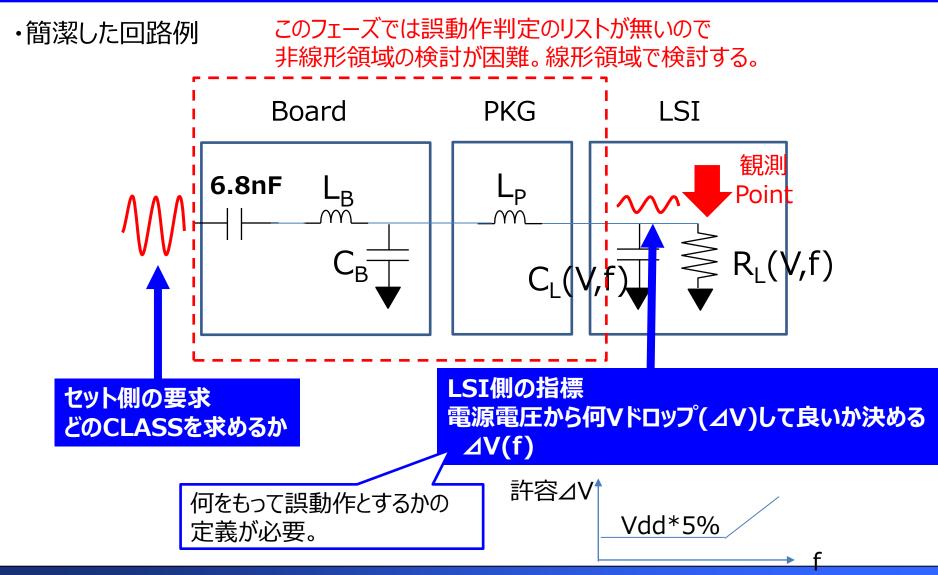

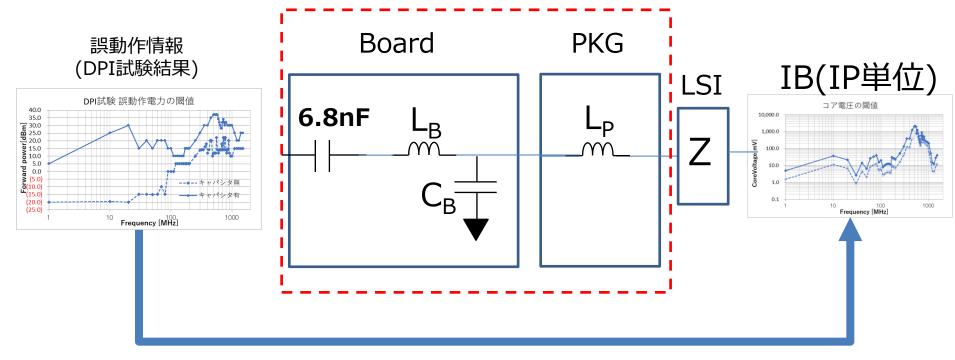

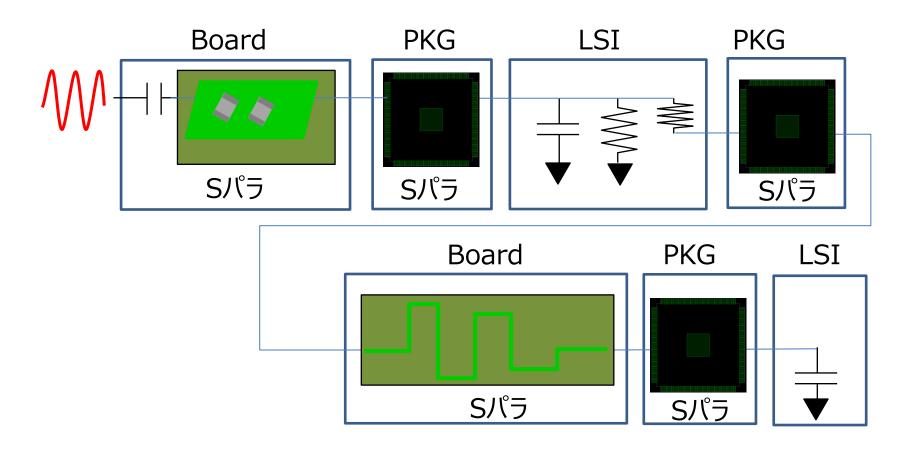

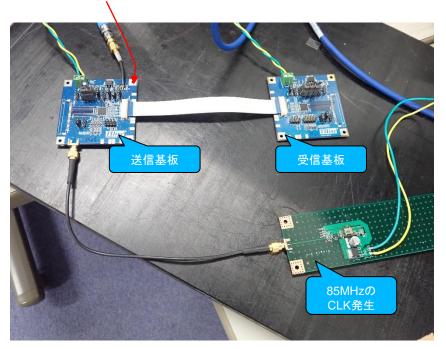

このフェーズはまだ物理形状が決まっていない状態なので、以下のような回路を組んで DPIを想定したシミュレーションを実施する。

- ・回路をどこまで簡潔にできるか?

- ・DPIのシミュレーションはどのように行うのか?

Timeドメインとして、ノイズを与え必要となるポイントの波形をシミュレーションで観測する?

その方が現象は分かりやすい。

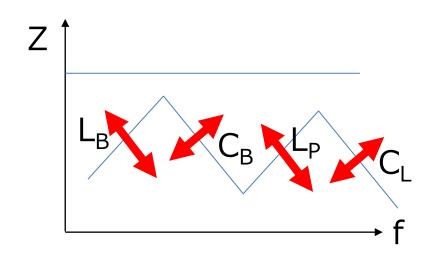

周波数ドメインとして、必要となるポイントまでの電源インピーダンスをシミュレーションで 観測するべきか?

その方が対策は分かりやすい。 この間の電源インピーダンス

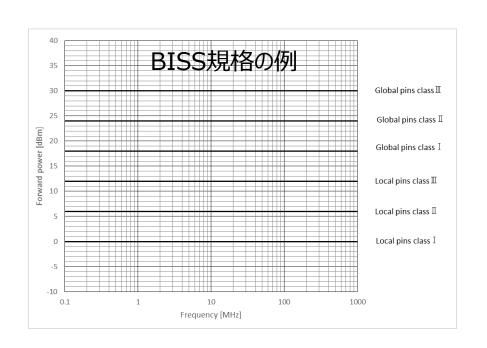

#### ・クライテリア

リップル⊿Vをクライテリアとした場合、印加電力と⊿Vの関係から、ターゲットの電源インピーダンスを決めることを検討する。

### ケース2. 過去評価実績のあるLSI設計の場合

#### ・簡潔した回路の例

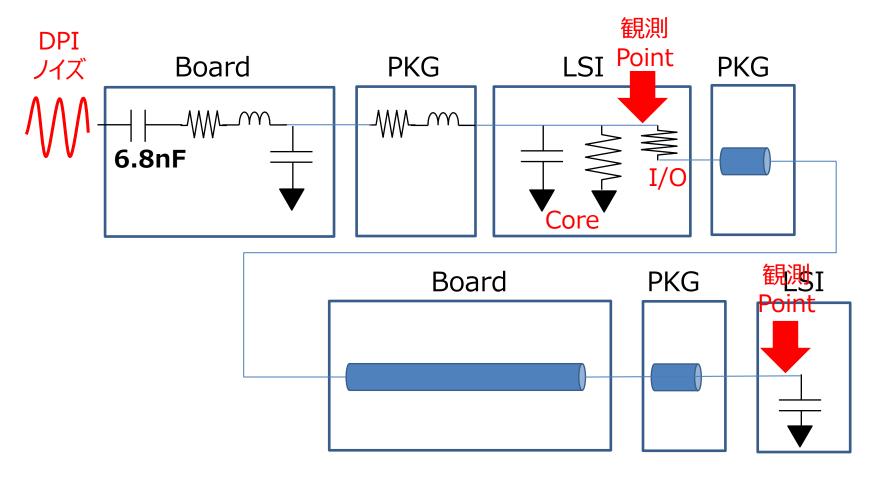

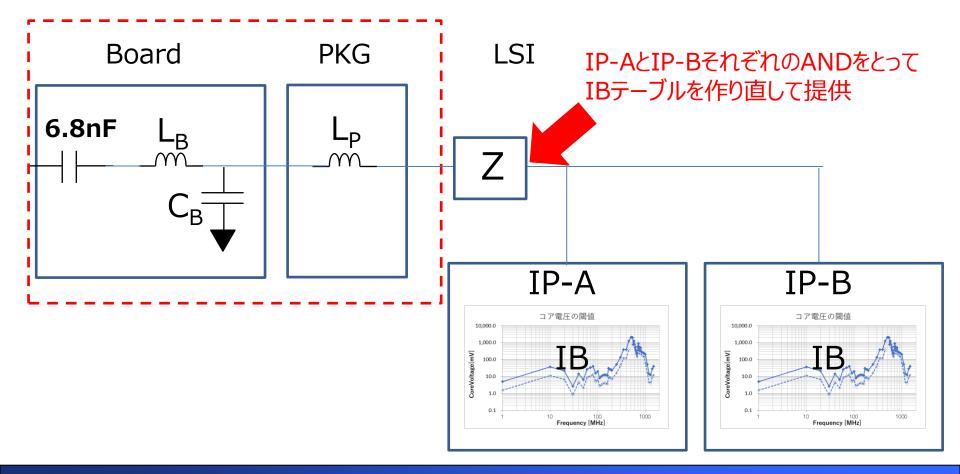

- ・DPI試験結果からIBを推定し、この情報を管理する。

- ・管理する際、LSI内はどのIP(複数の場合は全てのIP)に繋がっているかを 管理する。

・顧客に提供するときは、過去のIB情報をもとに、繋がる全てのIPのANDを取って Bump単位のIBテーブルを作り、セット側に提供する。

#### IEC62433 Part4

LPB-Cの中をシリーズにモデルを繋ぐことができるか?

→LPB-Cの中をVHDL-AMSで組んで、VHDL-AMS モデルをラッピングする

今後、IEC62433 Part4を用いた運用方法を検討する。

## における検証

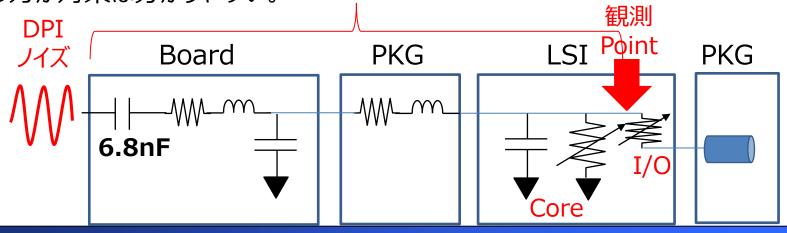

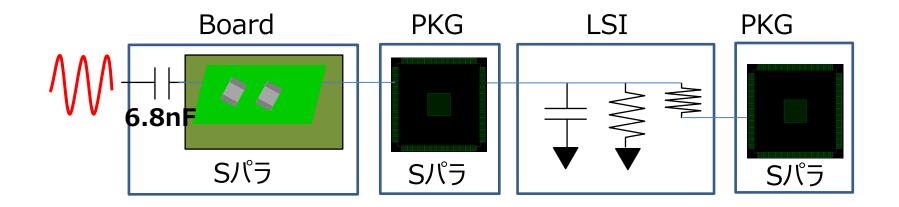

このフェーズは物理形状が決まってくるので、レイアウトデータから回路を組んで DPIを想定したシミュレーションを実施する。

### ・簡潔した回路の例

## における検証

### 電源インピーダンスの実測

# LPBライブラリ整備 TG

### ■LPBライブラリ整備 TG

『活動の目的』 LPBフォーマットのデータ流通およびそれを使った活用事例を紹介し、 LPBフォーマットの普及を図る。

- 『具体的取組』

- ・ディスクリートベンダーへWEB上にLPBフォーマットを公開するよう 働きかける。またそのサポートを行う。

- ・EDAベンダーにEDAツールへのLPBフォーマット入出力機能を搭載してもらうよう働きかける。

#### 『日程』

|           | 5月   | 6月         | 7月              | 8月            | 9月                | 10月      | 11月              | 12月          | 1月            | 2月             | 3月                         |             |

|-----------|------|------------|-----------------|---------------|-------------------|----------|------------------|--------------|---------------|----------------|----------------------------|-------------|

| LPB-SC    |      | /          | <b>▲</b> (6/19) |               |                   |          | <b>▲</b> (10/23) |              |               | <b>▲</b> (1/8) | <b>▲</b> (3/5              | 5)          |

| インフラ-TG @ | @WEB | <b></b> (/ | (6/5)           | <b>▲</b> (8/7 | <b>7)</b> ▲(8/28) |          | <b>▲</b> (10/16) | <b>▲</b> (12 | <u>2</u> /11) |                | <b>▲</b> (2/12) <b>▲</b> ( | (4/9)       |

| イベント      |      |            |                 |               | <b>(</b> 9        | 9/11-12) |                  | _            |               |                | <b>▲</b> (3/5              | 5)          |

|           |      |            |                 |               |                   | 合宿       |                  | J <u>E</u> ` | VeC?          | Design         | LPBフォー                     | <u>ーラ</u> / |

|           |      |            |                 |               |                   |          |                  |              |               | CON?           |                            |             |

|           |      | インフラ       | バG打ち合れ          | つせの中で         | 進捗状況を             | .確認し、フ   | フォローを行う。         |              |               |                |                            |             |