# ヘテロジーニアスインテグレーションをみんなで考えよう

## マルチチップインテグレーション調査TG

**Multi Chip Integration Investigation Technical Group**

主査 佐藤 ローム株式会社

- 1. はじめに

- 2. 23年度マルチチップインテグレーション調査TG活動サマリー

- 3. 調查報告

- 標準化団体

- TITAN Si<sup>2</sup>

- CDX

- UCIe

- IEEE EPS HIR (Heterogeneous Integration Roadmap)

- Motivation of Heterogeneous Integration

- Heterogeneous Integration Applications

- Heterogeneous Integration Roadmap Contents

- CHAPTER 5: AUTOMOTIVE

- CHAPTER 10: INTEGRATED POWER ELECTRONICS

- CHAPTER 13: CO DESIGN FOR HETEROGENEOUS INTEGRATION

- CHAPTER 14: MODELING AND SIMULATION

- 4. まとめ

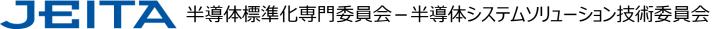

### ヘテロジーニアスインテグレーションとは?

Figure 6. Heterogeneous Integration and System in Package (SiP). Source: ASE

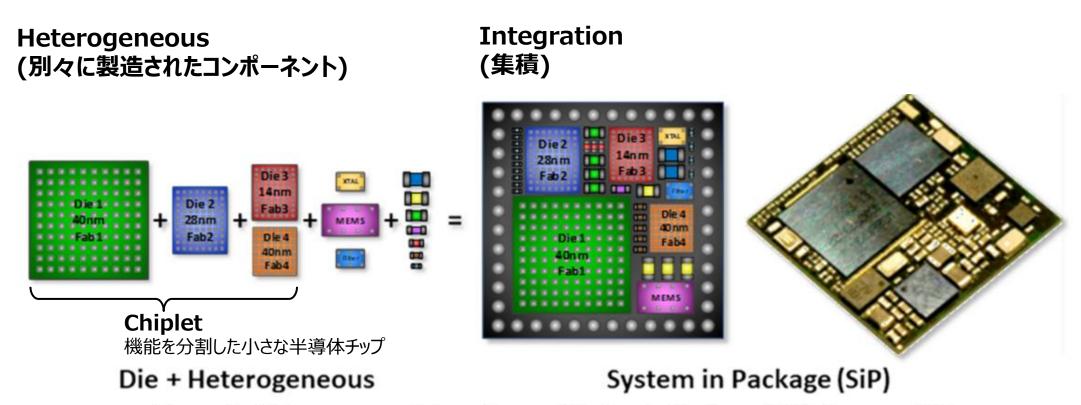

## 経産省の半導体・デジタル戦略(1/2)

出展:経済産業省 半導体デジタル戦略 令和5年6月

#### 2nm世代以降必須となるチップレット技術を確立

- 1chipの集積度ではMoore's lawについて行けない

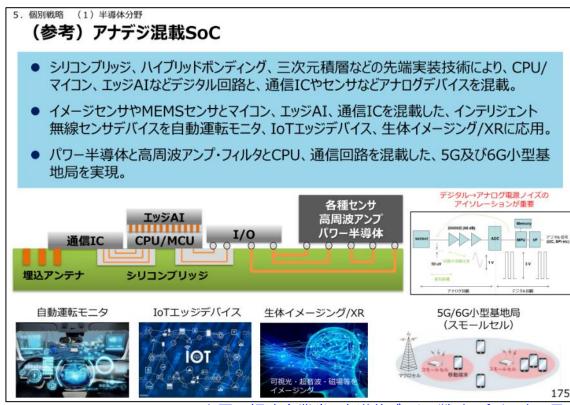

- アナデジ混載SoC

#### (参考) 先端パッケージ開発の先導・加速 ● 半導体の高性能化に向けて、微細化とともに1つの基板上にロジック半導体とメモリなど を実装するチップレット技術に注目が集まっている。 ● 2022年3月にはIntel, TSMC等がメンバーとなるチップレット標準化団体「UCIe」が設 立するなど、取組が加速しているが、実現には2.5D/3D実装技術等の進展が不可欠。 ● 我が国には世界有数の基板、材料、装置メーカが存在しており、JOINT等のコンソー シアムも活用して強化を進める。 ● 加えて、海外ファウンダリ・OSATとも連携して、先端材料・装置及び先端製造技術開 発を日本の地で進める。 ■Intelらが主導するチップレット新規格「UCIe」 ■先端パッケージの技術要素 2.5D/3DIC TSMCジャパン 3DIC研究開発センター 連携 引用:大日本印刷 誘致/連携 AMDA Grm & ASE GROUP Google Cloud Microsoft 製造技術 (放熱材、モールド材など) (再配線、接合など) 引用: UCIeホームページ SAMSUNG

出展:経済産業省 半導体デジタル戦略 令和5年6月

#### 2.5D/3D実装技術の進展が不可欠

・UCIeに注目

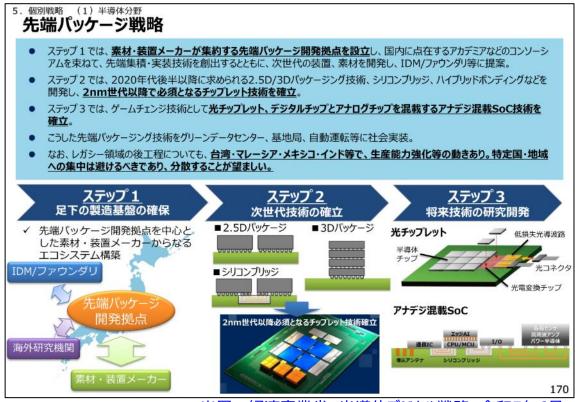

### 経産省の半導体・デジタル戦略(2/2)

出展:経済産業省 半導体デジタル戦略 令和5年6月

#### 先端集積・実装クラスターハブ拠点を構築

• LSTC先端パッケージ研究所を中心としたクラスターハブ構想

出展:経済産業省 半導体デジタル戦略 令和5年6月

#### アナデジ混載SoC

日本の半導体メーカーが入れる領域?

### JEITAでなにか標準化できることはないか?

### ■ マルチチップインテグレーション調査TG発足

- 技術動向調査

- 勉強会

- 課題の抽出

### ■ 調査対象

- 設計環境

- 熱検証

- 構造Sim

- 評価・テスト手法

- 電気特性(EMI,SI,PI)

- 戦略

- サプライチェーン

### ■ 体制

- 1. はじめに

- 2. 23年度マルチチップインテグレーション調査TG活動サマリー

- 3. 調查報告

- 標準化団体

- TITAN Si<sup>2</sup>

- CDX

- UCIe

- IEEE EPS HIR (Heterogeneous Integration Roadmap)

- Motivation of Heterogeneous Integration

- Heterogeneous Integration Applications

- Heterogeneous Integration Roadmap Contents

- CHAPTER 5: AUTOMOTIVE

- CHAPTER 10: INTEGRATED POWER ELECTRONICS

- CHAPTER 13: CO DESIGN FOR HETEROGENEOUS INTEGRATION

- CHAPTER 14: MODELING AND SIMULATION

- 4. まとめ

## 2.23年度マルチチップインテグレーション調査TG活動サマリー

## マルチチップインテグレーション調査TGの活動

第1回 2023年4月19日(水) 14:15~17:00

ハイブリッド(JEITA会議室、WebEX) ブレインストーミング

第2回 2023年5月17日(水) 10:00~12:00

WebEX

経産省資料読み合わせ

第3回 2023年6月19日(水)16:00~18:00

ハイブリッド(ローム会議室、WebEX)

TITANビデオ視聴・UCIe資料読み合わせ

第4回 2023年7月19日(水)10:00~12:00

ハイブリッド(JEITA会議室、WebEX)

EDAツールでできる事の紹介(シーメンスEDAジャパン眞篠さん)

第5回 2023年8月23日(水)10:00~12:00

ハイブリッド(ローム会議室、WebEX)

第1回~4回のまとめ、今後の進め方について

第6回 2023年9月20日(水)10:00~12:00

ハイブリッド(JEITA会議室、WebEX)

今後の進め方を南さん案をたたき台に議論する

第7回 2023年10月18日 (水) 10:00~12:00

ハイブリッド(JEITA会議室、WebEX)

ITC2023におけるチップレットに関するトピックス展開・ソニーのパブリック資料展開

第8回 2023年11月29日(水)10:00~12:00

ハイブリッド(ローム会議室、WebEX)

HIR資料の要約 (Introduction)

第9回 2023年12月20日(水)10:00~12:00

ハイブリッド(ローム会議室、WebEX)

HIR資料の要約 (INTEGRATED POWER ELECTRONICS)

第10回 2024年01月17日(水) 10:00~12:00

ハイブリッド(JEITA会議室、WebEX)

HIR資料の要約(Automotive +

CO DESIGN FOR HETEROGENEOUS INTEGRATION)

第11回 2024年02月14日(水) 10:00~12:00

ハイブリッド(ローム会議室、WebEX)

HIR資料の要約(MODELING AND SIMULATION)

第12回 2024年03月13日(水)10:00~12:00

ハイブリッド(JEITA会議室、WebEX)

24年度活動計画

### TG会議を年間12回開催

- 1. はじめに

- 2. 23年度マルチチップインテグレーション調査TG活動サマリー

- 3. 調査報告

- 標準化団体

- TITAN Si<sup>2</sup>

- CDX

- UCIe

- IEEE EPS HIR (Heterogeneous Integration Roadmap)

- Motivation of Heterogeneous Integration

- Heterogeneous Integration Applications

- Heterogeneous Integration Roadmap Contents

- CHAPTER 5: AUTOMOTIVE

- CHAPTER 10: INTEGRATED POWER ELECTRONICS

- CHAPTER 13: CO DESIGN FOR HETEROGENEOUS INTEGRATION

- CHAPTER 14: MODELING AND SIMULATION

- 4. まとめ

### 標準化団体

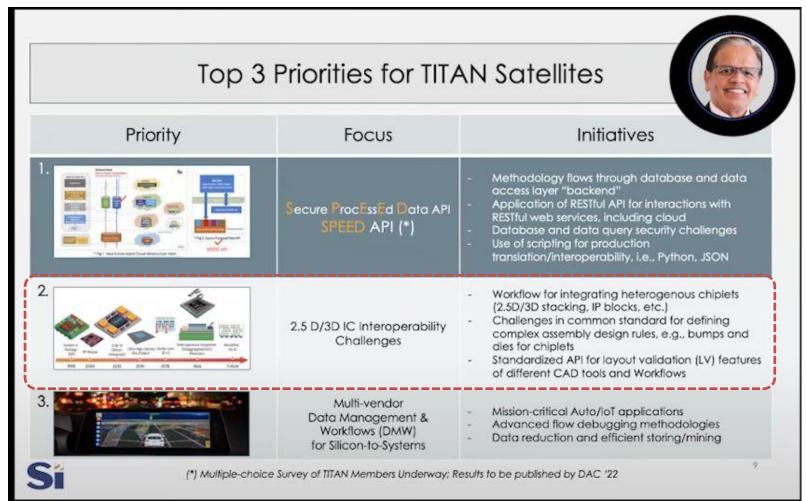

#### TITAN Si<sup>2</sup>

#### スコープ

- 異種チップレットを統合するためのワークフロー

- チップレットのバンプ・ダイ用の複雑なアセンブリルール

- 異なるCADツールで設計されたチップのレイアウト 検証用標準API

出展: TITAN ROUNDTABLE EVENT Friday, May 13, 2022

### 標準化団体

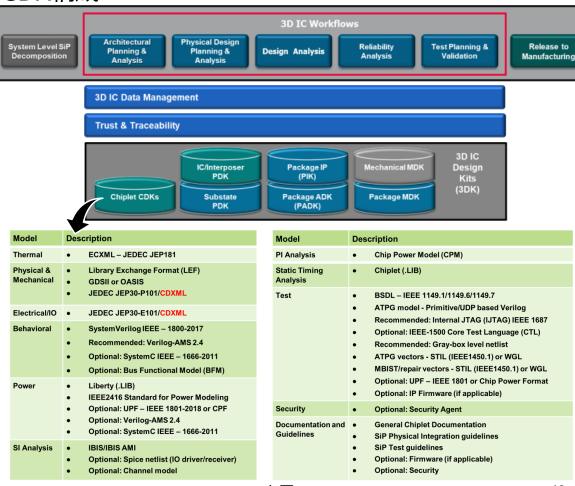

### **CDX** (Chiplet Design Exchange)

### **Chiplet Design Exchange (CDX)**

- CDX is a working group in the ODSA Project Group under Open Compute Group (OCP)

- · Charter: Recommend standardized chiplet models, workflows and ecosystem

- Members: EDA, chiplet Providers, Assemblers & Integrators

- Recent Activities

- Chiplet Design Kit Whitepaper (November 2021)

- JEP30/CDXML chiplet part model (January 2023)

- "Guide to Integration Workflows for Heterogeneous Chiplet Systems" (WIP)

- 3DK Initiative (WIP)

OCTOBER 17-19, 2023

Scaling Innovation Through Collaboration

#### スコープ

- 標準化されたチップレットモデル、ワークフロー、エコシステムの推奨

- Die-to-Dieインターフェイス等

#### **Chiplet Design Kit(CDK)**

**Recommended chiplet models to support 3DIC integration**

US Government Call for Standardized Assembly Design Kits (ADKs)

#### CDX構成

出展: OCP CDX-3DIC-Design-KITS.pdf

### 標準化団体

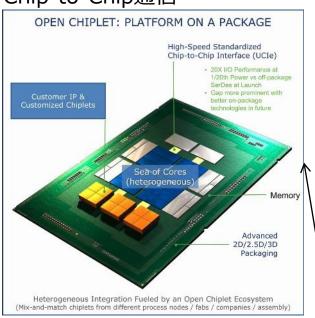

### **UCIe** (Universal Chiplet Interconnect Express)

Chip-to-Chip, Die-to-Die間の高速インターフェイスを通信プロトコルを含めて標準化

Chip-to-Chip通信

Die-to-Die通信

UCIe 1.0/1.1 Characteristics and Key Metrics

|                                   | STANDARD<br>PACKAGE            | ADVANCED<br>PACKAGE | COMMENTS                                                                                 |

|-----------------------------------|--------------------------------|---------------------|------------------------------------------------------------------------------------------|

|                                   | 4, 8, 12, 16, 24, 32           |                     | Lower speeds must be supported -interop (e.g., 4, 8, 12 for 12G device)                  |

| Width (each cluster)              | 16                             | 64                  | Width degradation in Standard, spare lanes in Advanced                                   |

| Bump Pitch (um)                   | 100 - 130                      | 25 - 55             | Interoperate across bump pitches in each package type across nodes                       |

| Channel Reach (mm)                | <= 25                          | <=2                 |                                                                                          |

| KPIs / TARGET FOR<br>KEY METRICS  | STANDARD<br>PACKAGE            | ADVANCED<br>PACKAGE | COMMENTS                                                                                 |

| B/W Shoreline (GB/s/mm)           | 28 - 224                       | 165 - 1317          | Conservatively estimated: AP: 45u; Standard: 110u; Proportionate to data rate (4G - 32G) |

| B/W Density (GB/s/mm²)            | 22-125                         | 188-1350            |                                                                                          |

| Power Efficiency target<br>(p3/b) | 0.5                            | 0.25                |                                                                                          |

| low-power entry/exit latence      | 0.5ns <=16G, 0.5-1ns >=24G     |                     | Power savings estimated at >= 85%                                                        |

| Latency (Tx + Rx)                 | < 2ns                          |                     | Includes D2D Adapter and PHY (FDI to bump and back)                                      |

| Reliability (FIT)                 | 0 < FIT (Failure In Time) << 1 |                     | FIT: #failures in a billion hours (expecting ~1E-30) w/ UCIe Flit Mode                   |

↑出展:ITC2023 Keynote

On-Package Chiplet Innovations with Universal Chiplet Interconnect Express(UCIe): Challenges and Opportunities

出展: UCIe

- 1. はじめに

- 2. 23年度マルチチップインテグレーション調査TG活動サマリー

- 3. 調査報告

- 標準化団体

- TITAN Si<sup>2</sup>

- CDX

- UCIe

- IEEE EPS HIR (Heterogeneous Integration Roadmap)

- Motivation of Heterogeneous Integration

- Heterogeneous Integration Applications

- Heterogeneous Integration Roadmap Contents

- CHAPTER 5: AUTOMOTIVE

- CHAPTER 10: INTEGRATED POWER ELECTRONICS

- CHAPTER 13: CO DESIGN FOR HETEROGENEOUS INTEGRATION

- CHAPTER 14: MODELING AND SIMULATION

- 4. まとめ

## **IEEE EPS HIR (Heterogeneous Integration Roadmap)**

# HETEROGENEOUS INTEGRATION ROADMAP

#### エレクトロニクス業界に長期的なビジョンを提供

- 将来の困難な課題と潜在的な解決策を推定

- 世界の展望と戦略的技術要件を包括的に把握

#### 対象

専門家、産業界、学術界、研究機関

#### ロードマップ

今後 15 年間のエレクトロニクス業界の進化を分析し、25 年のビジョンを提供

- 新しいデバイスと新しい材料の統合するための長期的な研究開発スケジュールを立てることができる。

- 業界のコラボレーションにより進歩のペースを加速する

#### HIR チーム

エレクトロニクスエコシステムの複雑さに関する22のテクニカルワーキンググループで構成 (産業界、学界、組織全体から重要な専門家を集めたボランティア活動)

#### スポンサー

IEEE(Electronics Packaging Society, Electron Devices Society, Photonics Society), SEMI, ASME EPPD

### **Motivation of Heterogeneous Integration**

####

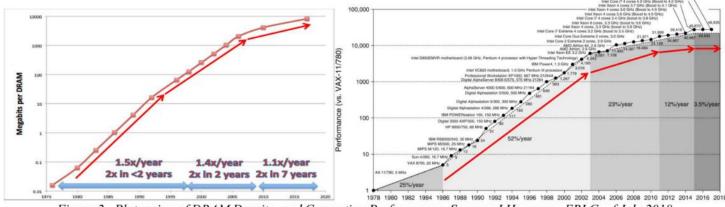

Figure 2. Plateauing of DRAM Density, and Computing Performance. Source: J Hennessy, ERI Conf July 2018

##

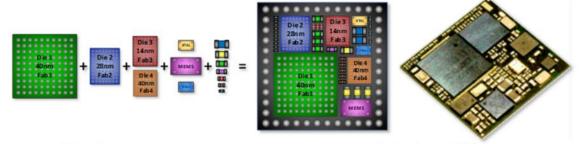

#### ❷ 解決策

#### **Heterogeneous Integration**

Die + Heterogeneous

System in Package (SiP)

ムーアの法則のスケーリングが遠い未来まで拡大する

#### **Benefit**

- より高いパフォーマンス

- より低いレイテンシー

- 小型化

- 軽量化

- 機能あたりの電力の低減

- ・ 歩留まり向上によるコストの削減

出展: IEEE EPS HIR

半導体標準化専門委員会ー半導体システムソリューション技術委員会

### **Heterogeneous Integration Applications**

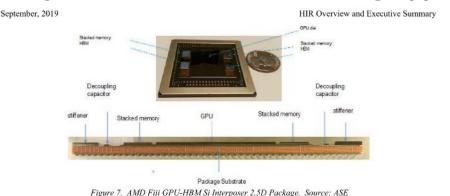

1) AMD's Fiji GPU with 4 HBM for Gaming Application

4つのHBMを搭載したAMDのフィジーGPU ASEで最初に2016年にゲームアプリケーション向けに 生産されている

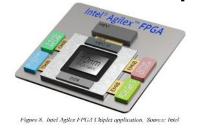

2) Intel's Agilex FPGA in a chiplet application

組み込みマルチダイインターコネクトブリッジ (EMIB) テクノロジーが適用されている

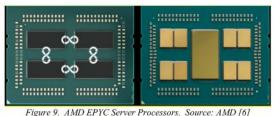

#### **AMD's EPYC Server Processors**

大規模なモノリシック SoC をより小さな SoC に分割 AMDがシリコンインターポーザー上で初めて実証した

### **Heterogeneous Integration Applications**

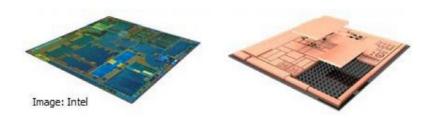

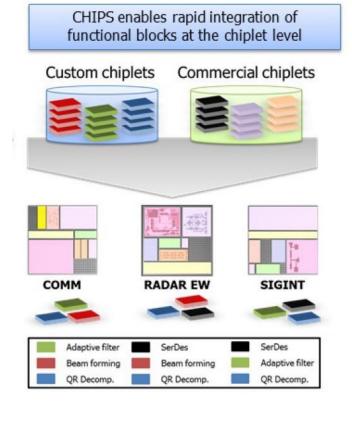

3) The CHIPS program is an important part of the DARPA Electronics Resurgence Initiative (ERI)

helping drive HI.

Figure 10. DARPA CHIPS Program. Source: DARPA

#### ERIの構造&DARPAの図

既存および新規のIPブロックを使用してシステムを組み立てることができる、個別のモジュラーIPブロックのエコシステム統合テクノロジー

\*JUMP: Joint University Microelectronics Program

#### **Heterogeneous Integration Applications**

4) For Smart Phone

#### Apple A12 Processor

#### Samsung EXYNOS 9810

#### Huawei HiSilicon Kirin 980

Figure 11. Three examples of Package on Package [PoP] in Smart Phone Teardowns.

Source: Prismak Partners & Bingahmton University

#### スマートフォン業界

何世代にもわたって SiP の使用においてHeterogeneous Integrationテクノロジーをいち早く採用小型化、共同設計のためのモジュール性、および世代間の強化

## **IEEE EPS HIR (Heterogeneous Integration Roadmap)**

### **Heterogeneous Integration Applications**

5) WLP Fan-In and Fan-Out

製造時に2つのダイが近接して配置された基板上のファンアウトチップ。

Figure 12. Fan-Out Chip on Substrate (HIR WLP Chapter, Figure 9)

6) 3D Multi-stack (MUST) system integration technology

Figure 13. Fan-Out Multi-Stack integration (TSMC MiM). (WLP Chapter Figure 38, and ECTC 2019)

### **Heterogeneous Integration Applications**

7) The SiP integration of Wide-Band-Gap (WBG) power semiconductors such as silicon carbide (SiC) and gallium-nitride

Figure 14. Example of EMI-optimized SiP SiC Module. Source: Fraunhofer IZM

#### 組み込みSiCモジュール

非常に低い寄生インダクタンス 非常に優れた高速スイッチング フェイスアップおよび反転されたダイが基板に組み立てられ、 エポキシプリプレグ層に埋め込まれる

#### 8) Samsung Galaxy S10

SAMSUNG GALAXY S10 mmWave 5G ANTENNA MODULES

3つの異なるアンテナモジュールがフレームの周囲に配置されており、フレームの底部近くに2G/3G/4Gアンテナモジュールがある

Figure 15. Samsung Galaxy 10 teardown showing 5G antennas. Source: Prismak Partners & Bingahmton University

<u>出展: IEEE EPS HIR</u>

## **IEEE EPS HIR (Heterogeneous Integration Roadmap)**

### **Heterogeneous Integration Roadmap Contents**

CHAPTER 1 : HETEROGENEOUS INTEGRATION ROADMAP – OVERVIEW CHAPTER 2 : HIGH PERFORMANCE COMPUTING AND DATA CENTERS

CHAPTER 3 : THE INTERNET OF THINGS (IOT)

CHAPTER 4 : MEDICAL, HEALTH & WEARABLES

CHAPTER 5 : AUTOMOTIVE

CHAPTER 6 : AEROSPACE AND DEFENSE

CHAPTER 7 : MOBILE

CHAPTER 8 : SINGLE CHIP AND MULTI CHIP INTEGRATION

CHAPTER 9 : INTEGRATED PHOTONICS

CHAPTER 10 : INTEGRATED POWER ELECTRONICS

CHAPTER 11 : MEMS AND SENSOR INTEGRATION

CHAPTER 12 : 5G COMMUNICATIONS

CHAPTER 13 : CO DESIGN FOR HETEROGENEOUS INTEGRATION

CHAPTER 14 : MODELING AND SIMULATION

CHAPTER 15 : MATERIALS AND EMERGING RESEARCH MATERIALS

CHAPTER 16 : EMERGING RESEARCH DEVICES

CHAPTER 17 : TEST TECHNOLOGY

CHAPTER 18 : SUPPLY CHAIN

CHAPTER 19 : SECURITY CHAPTER 20 : THERMAL

CHAPTER 21 : SIP AND MODULE SYSTEM INTEGRATION

CHAPTER 22 : INTERCONNECTS FOR 2D AND 3D ARCHITECTURES

CHAPTER 23 : WAFER-LEVEL PACKAGING (WLP)

<mark>ハイライト部</mark>を調査

**CHAPTER 5: AUTOMOTIVE**

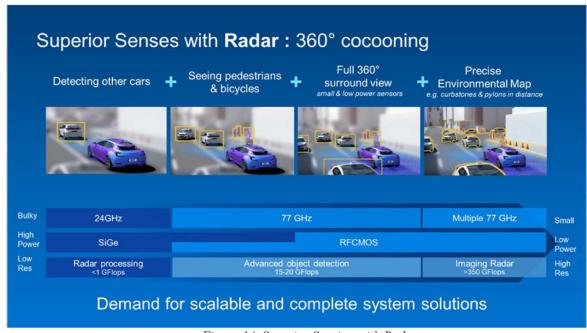

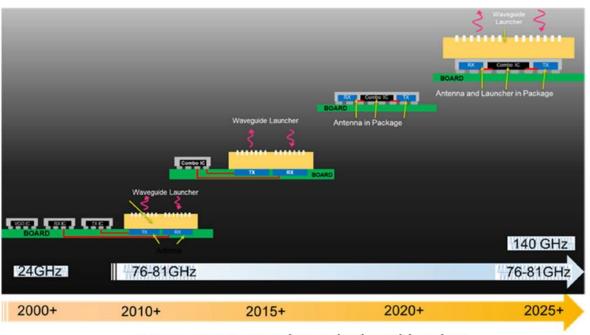

Pickup: Radar

Figure 14. Superior Sensing with Radar

Figure 20. RF Frequency Evolution and Radar Module Evolution

## **IEEE EPS HIR (Heterogeneous Integration Roadmap)**

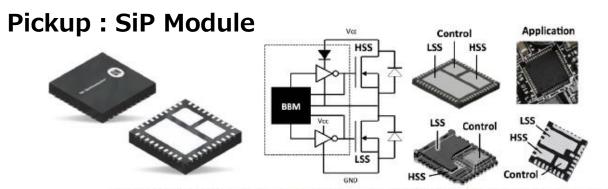

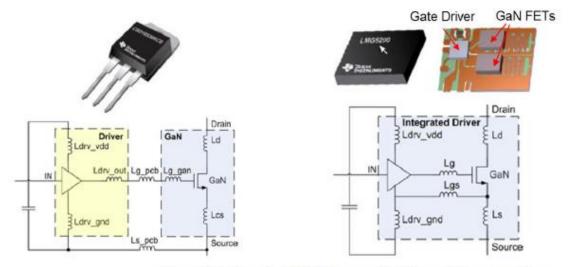

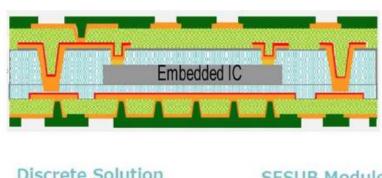

#### **CHAPTER 10: INTEGRATED POWER ELECTRONICS**

Figure II-6: Control, high-side switch and low-side switch integration in leadframe packages.

Figure II-7: Integrated GaN drivers and switches on the same package.

Figure II-11. Texas Instruments' MicroSiP DC-DC module [14] and TDK's SESUB Package.

## **IEEE EPS HIR (Heterogeneous Integration Roadmap)**

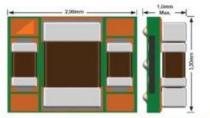

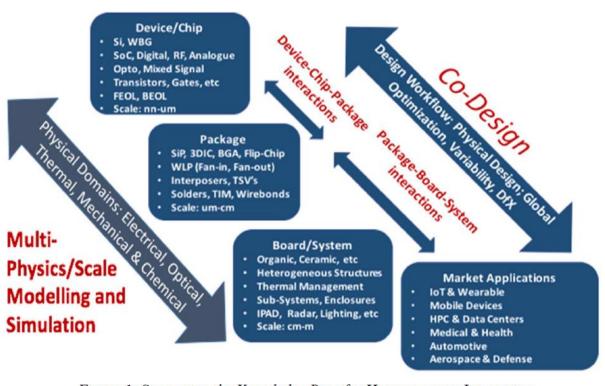

**CHAPTER 13: CO DESIGN FOR HETEROGENEOUS INTEGRATION**

**Pickup: System Co-Design**

Figure 1. Domains in Co-Design Environment (Source [1]).

#### LSIの設計

PackageやBoardを考慮していない

### Heterogeneous Integrationの設計

LPB協調設計が必要

- ・ 物理的および論理的な相互作用に関する制約を満たす

- LSI、Package、Board(PCB)の組み立ておよび最適化

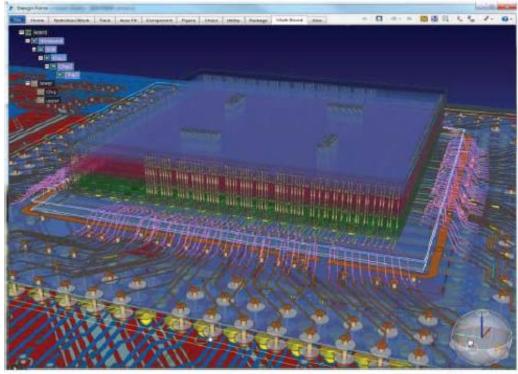

## **IEEE EPS HIR (Heterogeneous Integration Roadmap)**

**CHAPTER 14: MODELING AND SIMULATION**

Pickup: Multi-Physics / Scale Modelling and Simulation

Figure 1: Supporting the Knowledge Base for Heterogeneous Integration

#### 現在のM&S解析

- 単一物理(電気、光学、熱、機械、化学)

- 単一ドメイン (ダイ、パッケージ、またはボード/システム)

### Heterogeneous IntegrationのM&S解析

- マルチフィジックス/スケール機能

- ダイ-パッケージ-ボード/システム協調設計システム

- 1. はじめに

- 2. 23年度マルチチップインテグレーション調査TG活動サマリー

- 3. 調查報告

- 標準化団体

- TITAN Si<sup>2</sup>

- CDX

- UCIe

- IEEE EPS HIR (Heterogeneous Integration Roadmap)

- Motivation of Heterogeneous Integration

- Heterogeneous Integration Applications

- Heterogeneous Integration Roadmap Contents

- CHAPTER 5: AUTOMOTIVE

- CHAPTER 10: INTEGRATED POWER ELECTRONICS

- CHAPTER 13: CO DESIGN FOR HETEROGENEOUS INTEGRATION

- CHAPTER 14: MODELING AND SIMULATION

- 4. まとめ

## 23年度Heterogeneous Integration調査のまとめ

- ・ Heterogeneous Integrationのメリット

- より高いパフォーマンス

- より低いレイテンシー

- 小型化

- 軽量化

- 機能あたりの電力の低減

- 歩留まり向上によるコストの削減

- Heterogeneous Integrationの課題

- LPB協調設計(SI、PI、EMC、熱)

- マルチフィジックスM&S環境(=連成解析)

- パッケージの反りや放熱の問題の解決

- 組立技術

- 組立コスト

## 24年度活動計画

- 世界の動向の継続的観察と調査

- HIR資料の調査継続

- 標準化活動の検討

- 日本の事業への有効性考察としてケーススタディー実施

- アライアンス参加検討およびパートナー見極め

# みなさん、一緒に活動しませんか!

参加企業募集中