#### IBIS活用TGからご報告

DCDCコンバータのIBISモデルを使用した CISPR25伝導ノイズSim試行 ~Sim出力波形のリンギング原因対策~

モデルベースデザイン/システム設計WG IBIS活用TG 坂田和之

- 背景と目的

- 実測によるDCDCコンバータのインピーダンスモデル作成

- 実測環境と実測結果

- シミュレーション結果と実測比較

- 実測との誤差が大きい原因検討

- IBISモデルからSpiceマクロモデル生成

- Spiceマクロモデル改良

- まとめ

- 今後の課題と活動内容

#### 背景と目的

パワーデバイスモデルの多くは、特定の回路シミュレータ用Spiceモデルで提供

→回路シミュレータに制限がある

パワーデイバスモデルをIBISで実現できれば

→回路シミュレータの制限がなくなり、利便性が向上

さらに、実測からIBISモデルを作成できれば

→モデル作成が容易になる。

IBIS活用TGでは、パワーデバイスの一つであるDCDCコンバータをIBIS化し、EMIシミュレーション※への適用可能性を検討中

本発表では、2019年LPB Forumで報告したIBIS化したDCDCコンバータを用いたシミュレーションにおける実測との誤差要因について考察する。

※CISPR25伝導ノイズシミュレーション

- 背景と目的

- 実測によるDCDCコンバータのインピーダンスモデル作成

- 実測環境と実測結果

- シミュレーション結果と実測比較

- 実測との誤差が大きい原因検討

- IBISモデルからSpiceマクロモデル生成

- Spiceマクロモデル改良

- ・まとめ

- 今後の課題と活動内容

# DCDC コンバータのインピーダンス測定

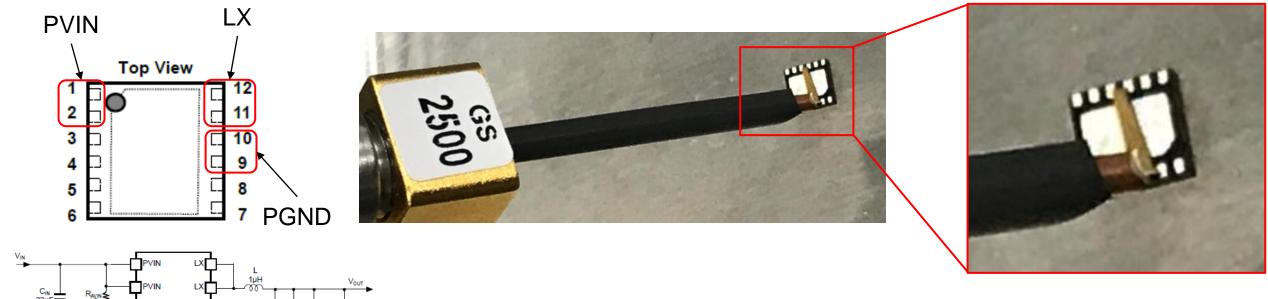

DCDC converter: RICOH RP510L004N-TR-A

#### IO Pins for impedance measurement

| Pin(S-G)  | No.(S-G)    | Pitch(mm)    | Bias voltage(V)             | Freq.(Hz)※ |

|-----------|-------------|--------------|-----------------------------|------------|

| PVIN-PGND | PIN2-PIN10  | 2.65mm±0.3mm | 0,0.3,0.6,1,2,3,3.6,4,5,5.5 | 1k-3G      |

| PVIN-LX   | PIN2-PIN11  | 2.6mm±0.3mm  | 0,0.3,0.6,1,2,3,3.6,4,5,5.5 | 1k-3G      |

| LX-PGND   | PIN11-PIN10 | 0.5mm±0.1mm  | 0,0.3,0.6,1,2,3,3.6,4,5,5.5 | 1k-3G      |

本報告での使用装置:HP4291A

cf.) https://www.e-devices.ricoh.co.jp/en/products/power/dcdc/rp510/rp510-ea.pdf

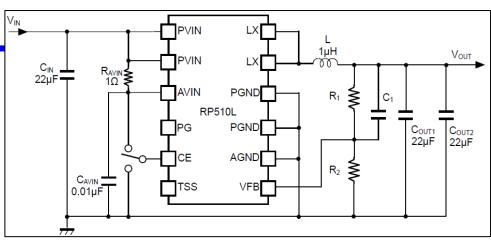

**Typical Application Circuit**

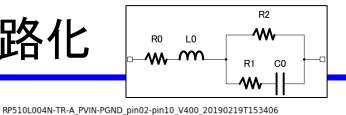

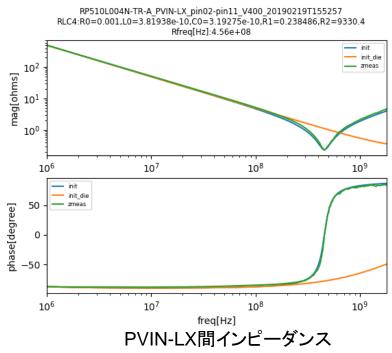

# インピーダンス実測と等価回路化

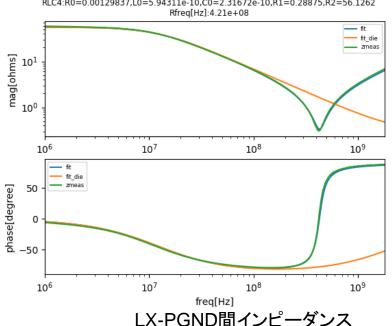

RP510L004N-TR-A\_2\_LX-PGND\_pin11-pin10\_V500\_20190219T165129 RLC4:R0=0.00129837,L0=5.94311e-10,C0=2.31672e-10,R1=0.28875,R2=56.1262 Rfreq[Hz]:4.21e+08

Rfreq[Hz]:8.17e+08 - fit\_die \_\_\_ zmeas [smho]gm 10<sub>1</sub> 10<sup>0</sup> 10<sup>6</sup> 10<sup>7</sup> 108 10<sup>9</sup> 50 phase[degree] 10<sup>6</sup> 10<sup>7</sup> 108 10<sup>9</sup> freq[Hz]

RLC4:R0=0.663538,L0=1.86253e-10,C0=1.85708e-10,R1=0.00560028,R2=1.87806e+07

(HighSide)

LX-PGND間インピーダンス (LowSide)

L(nH) C(pF)  $R(\Omega)$ Rleak(Ω) **PVIN-PGND** 0.19 186 0.66 1.87e7 **PVIN-LX** 0.38 319 0.24 9339 LX-PGND 0.59 232 0.29 56.12

直列容量 134pF

PVIN-PGND間インピーダンス

**PVIN-PGND** 186p-134p=52pF

#### IBISファイル中の容量記述

実測した容量をIBIS内のC\_comp\_pullup、C\_comp\_pulldownに記載

今回はリコー電子デバイス様のモデリング精度が高く、容量がほぼ一致しているので問題ないが、 大きくずれていた場合はspiceネットに容量を追加してIBISを作成しなおす必要がある。

- 背景と目的

- 実測によるDCDCコンバータのインピーダンスモデル作成

- 実測環境と実測結果

- シミュレーション結果と実測比較

- ・ 実測との誤差が大きい原因検討

- IBISモデルからSpiceマクロモデル生成

- Spiceマクロモデル改良

- ・まとめ

- 今後の課題と活動内容

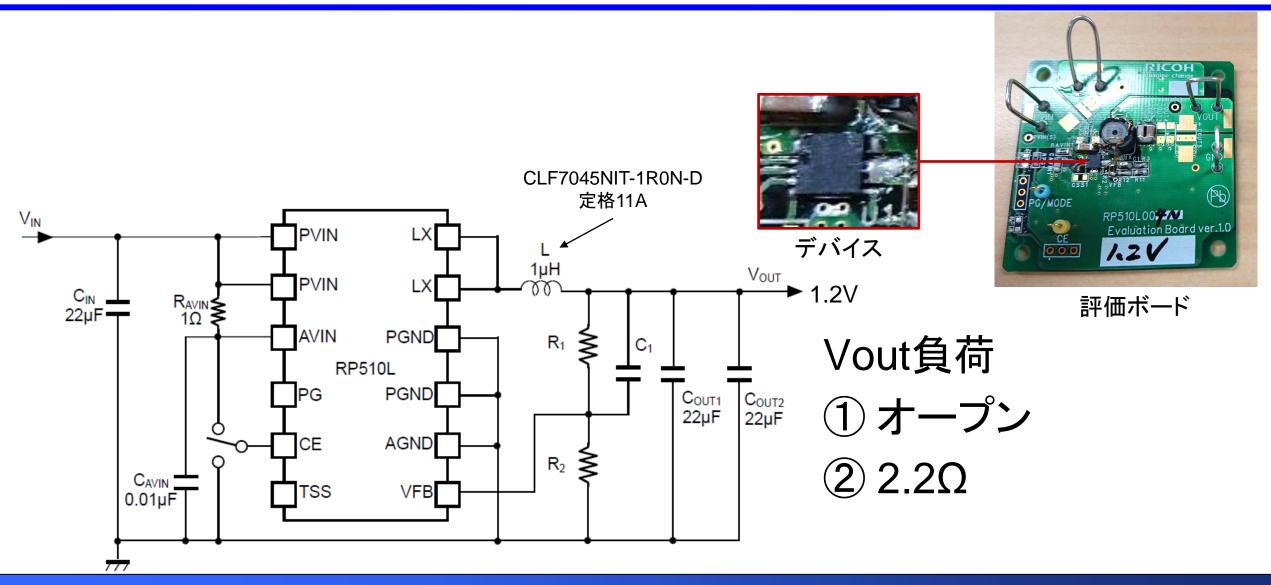

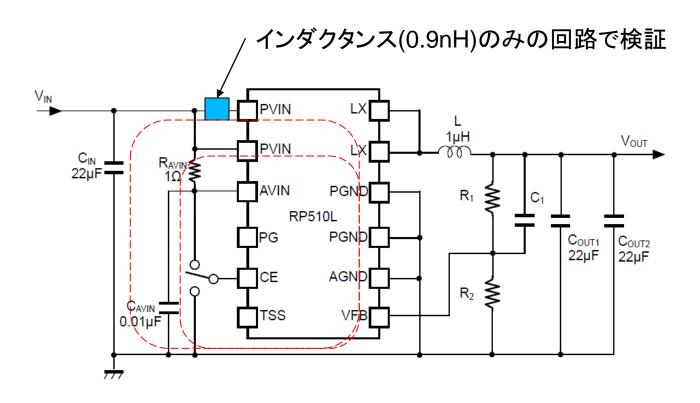

# 測定用回路構成

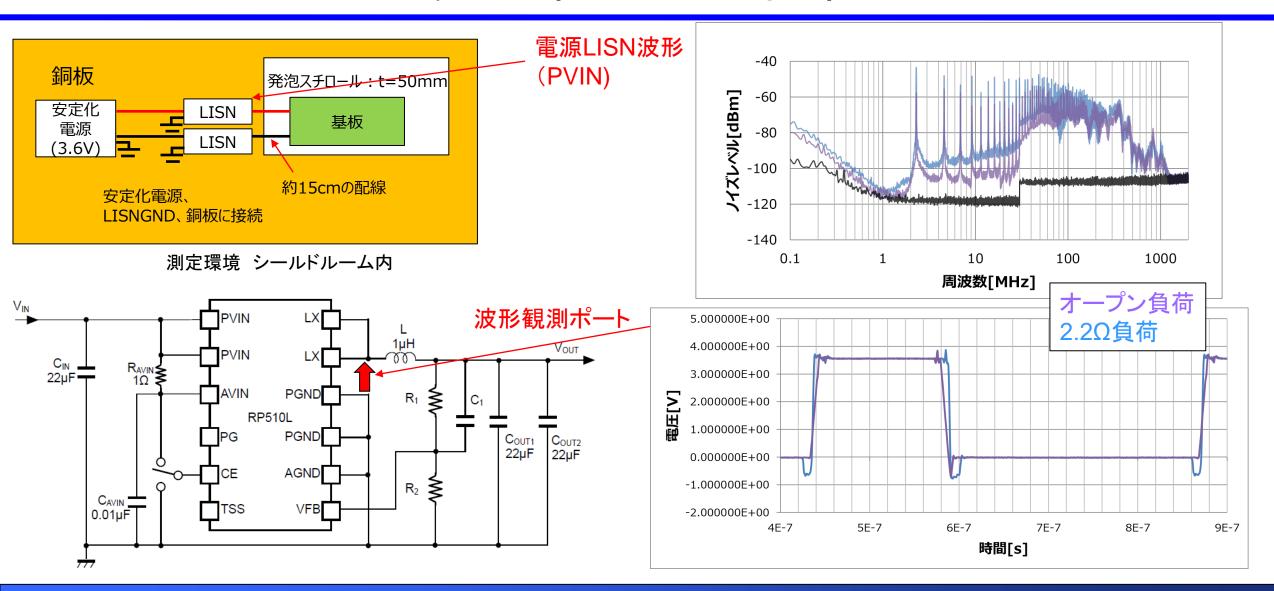

# 実測環境および結果

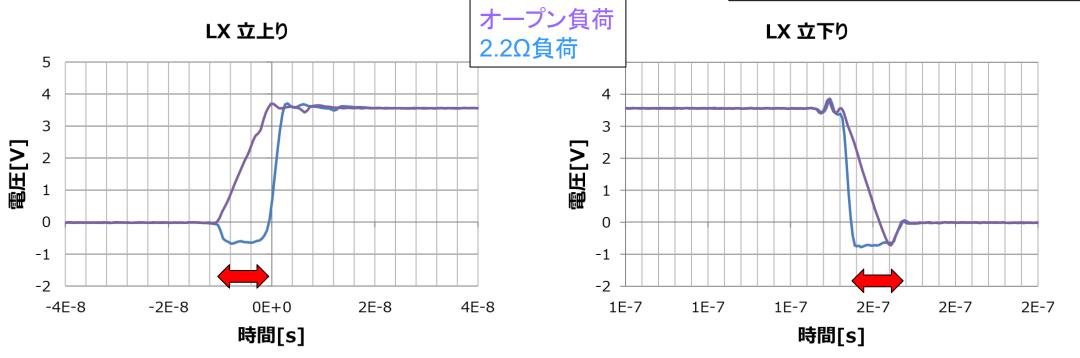

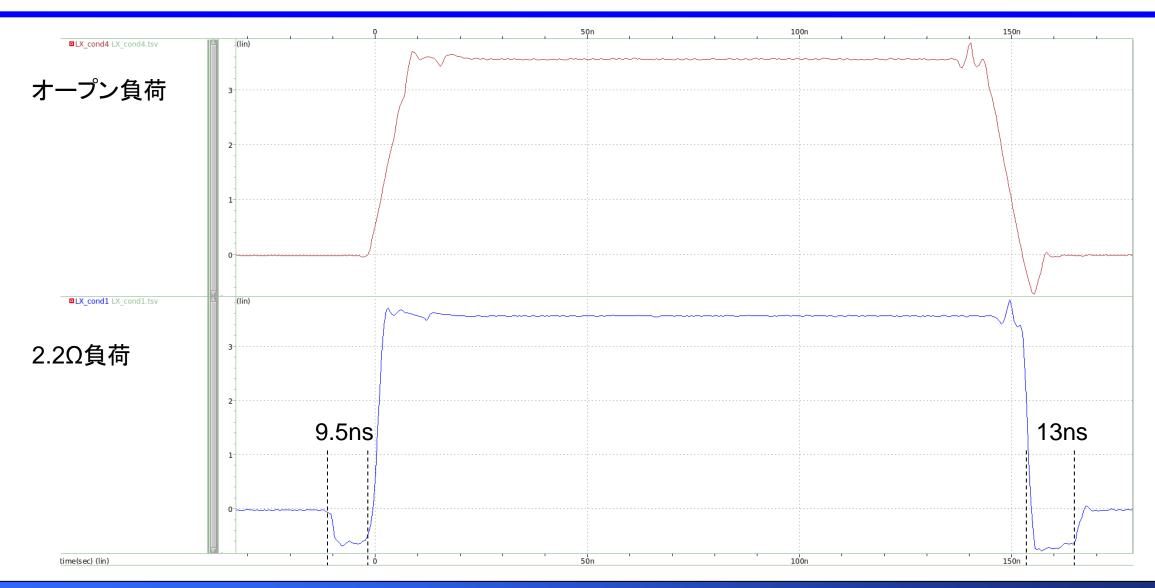

# LX実測波形

抵抗負荷ではLX波形にデッドタイムが表れている。

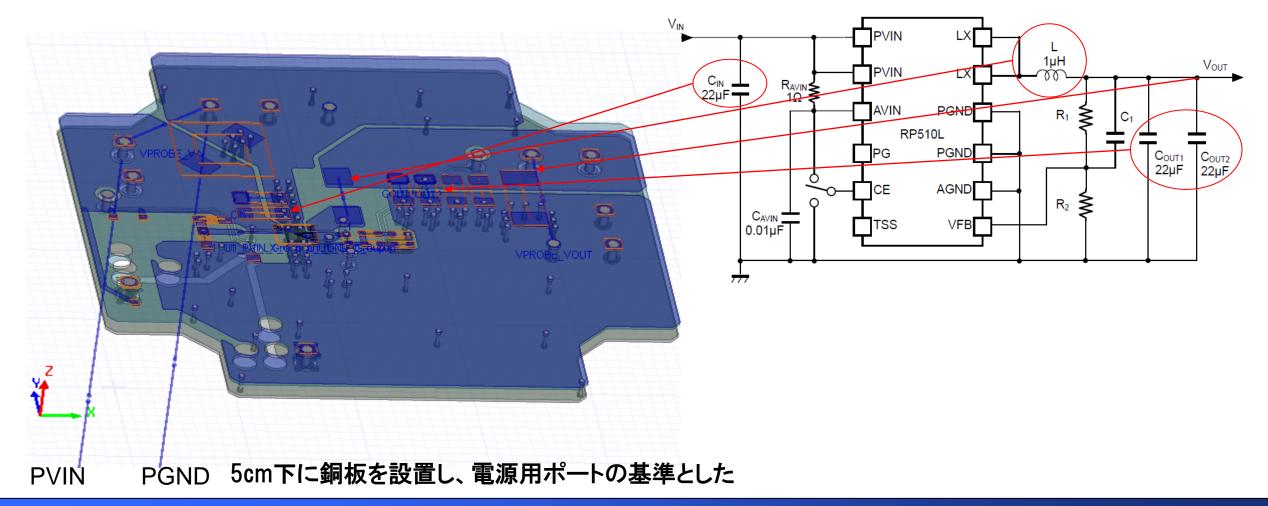

# プリント基板モデル

# プリント基板を電磁界解析ツールでモデリング

- 背景と目的

- 実測によるDCDCコンバータのインピーダンスモデル作成

- 実測環境と実測結果

- ・ シミュレーション結果と実測比較

- 実測との誤差が大きい原因検討

- IBISモデルからSpiceマクロモデル生成

- Spiceマクロモデル改良

- ・まとめ

- 今後の課題と活動内容

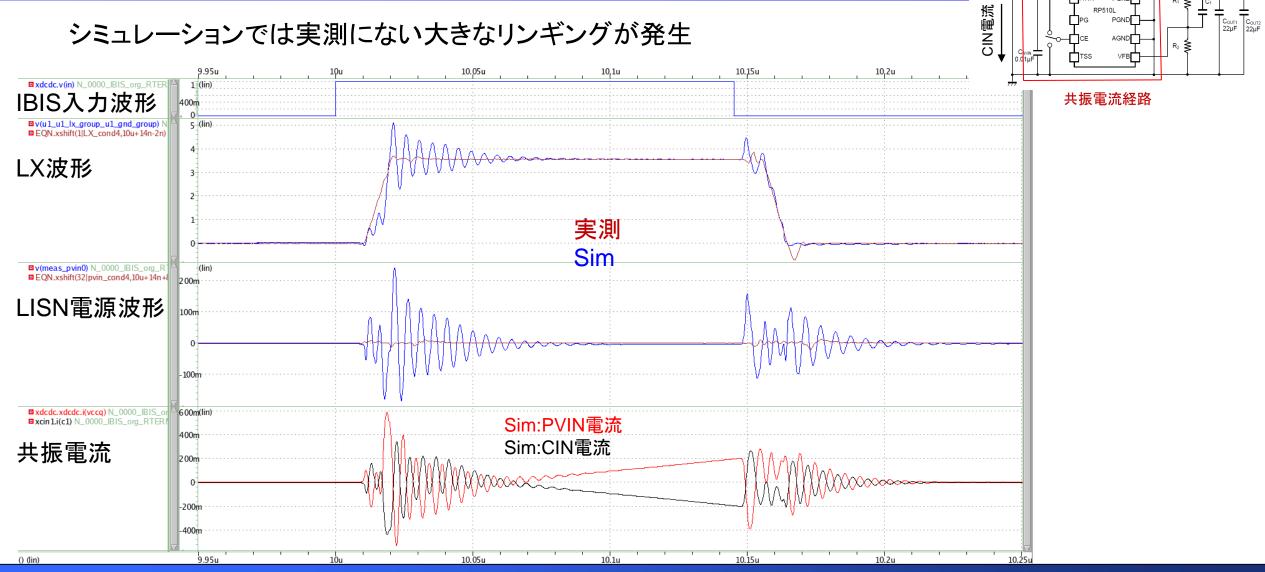

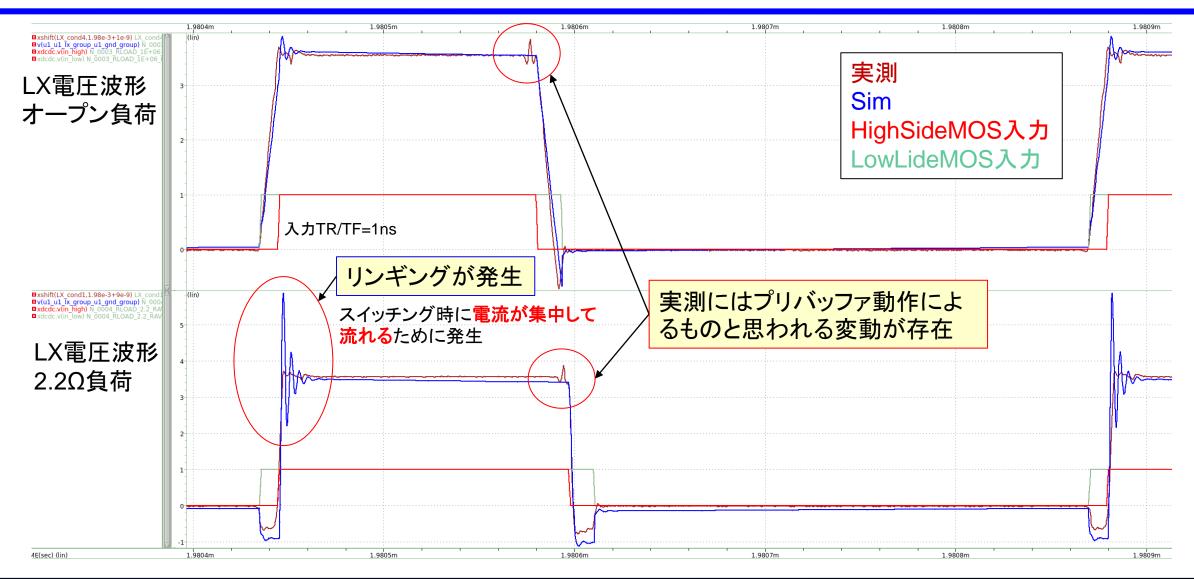

# シミュレーション結果:オープン

#### シミュレーションでは実測にない大きなリンギングが発生

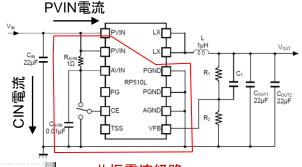

PVIN電流

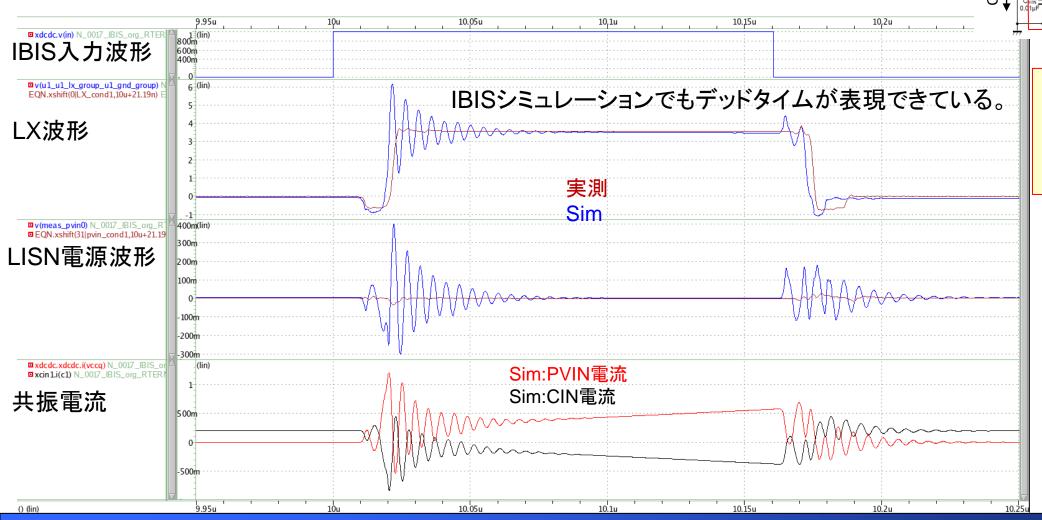

# シミュレーション結果:抵抗負荷

オープン終端同様、シミュレーションでは実測にない大きなリンギングが発生

共振電流経路

PVIN,PGND,CIN,C AVINを通る共振電 流によりリンギング が発生している。

# PVIN伝導ノイズ波形(オープン)

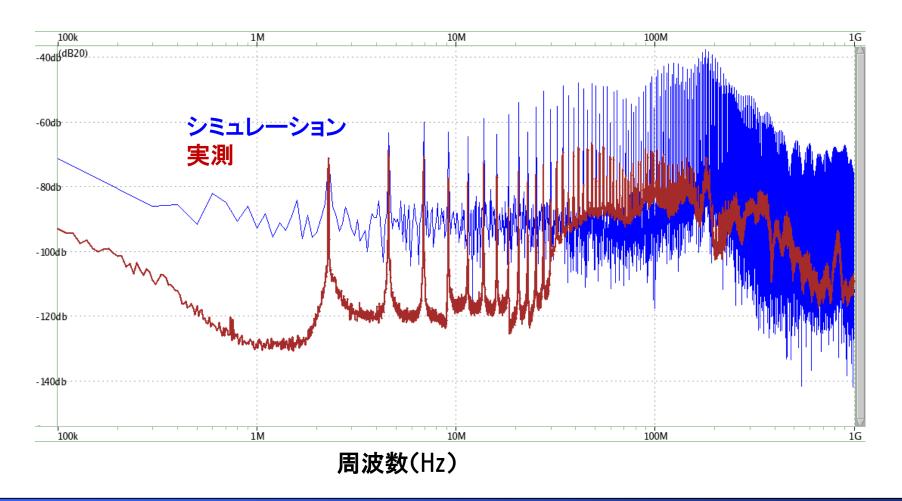

#### シミュレーションのピークは実測よりも最大30db大きい

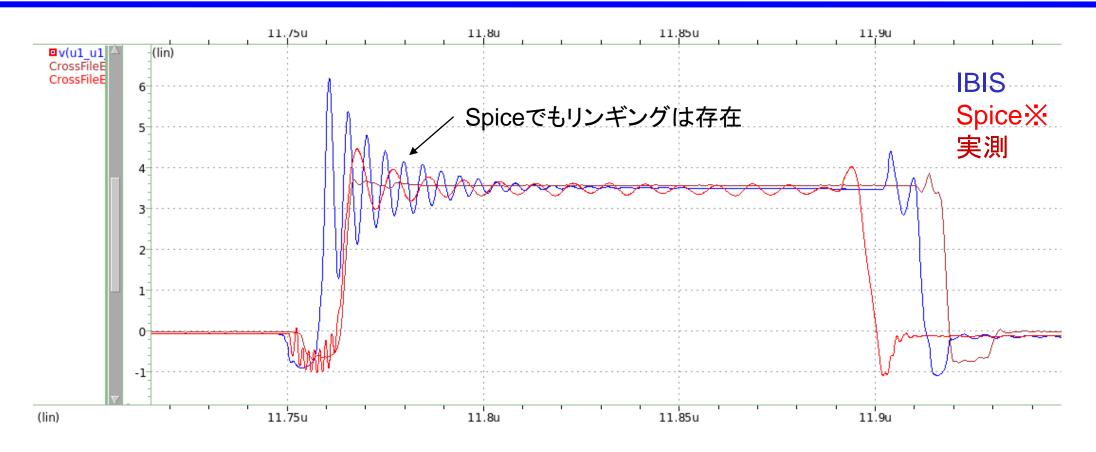

# LX(出力端子) 電圧波形: Spice、IBISと実測比較

Spiceでもリンギングは発生している。 まずは、このリンギングを解決することから始め、解決後に実装モデルの検討に入る。

※チューニング前で、実負荷抽出していないspiceネット

- 背景と目的

- 実測によるDCDCコンバータのインピーダンスモデル作成

- 実測環境と実測結果

- シミュレーション結果と実測比較

- 実測との誤差が大きい原因検討

- IBISモデルからSpiceマクロモデル生成

- Spiceマクロモデル改良

- ・まとめ

- 今後の課題と活動内容

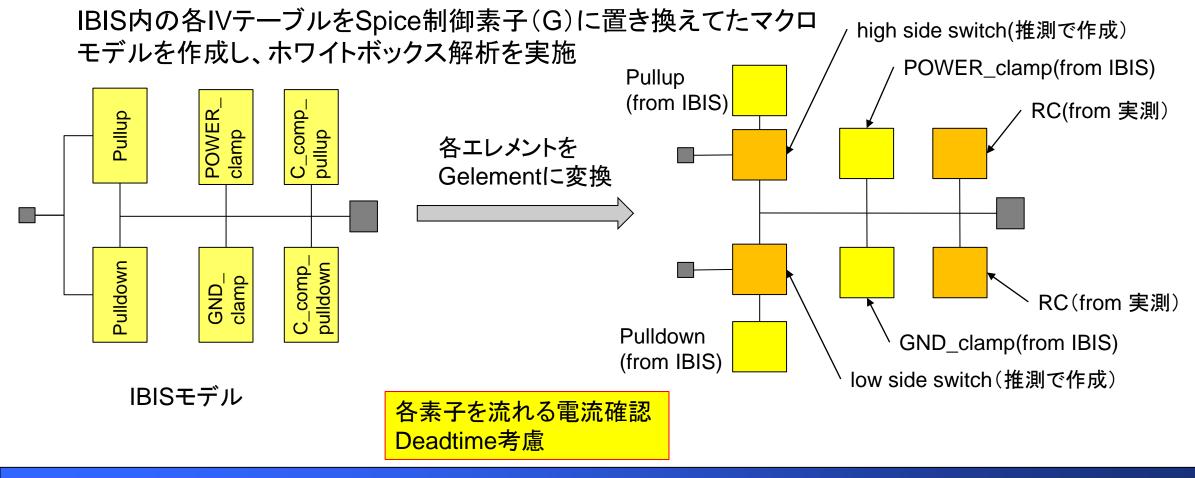

# IBISモデルからSpiceマクロモデル生成

回路シミュレータによるIBIS解析はブラックボックス解析になるため、

原因検討が困難。

# シンプル実装モデル

検討を簡単にするために、Sパラ実装モデルからPVIN電源インダクタンスのみ考慮のシンプル実装モデルに変更

電磁界解析モデルより CINループのインダクタンス:0.88nH CAVINループのインダクタンス:2.17nH

# 実測波形からDeadtimeの見積もり(LX電圧波形)

# SpiceマクロモデルのSim結果(シンプル実装モデル)

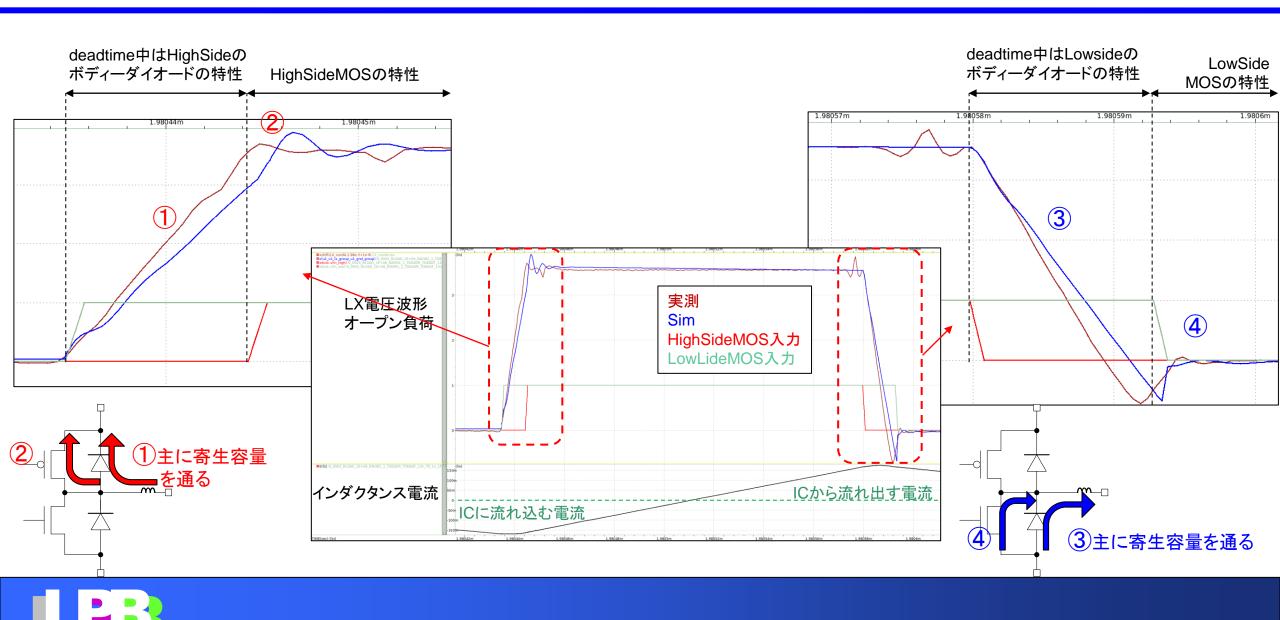

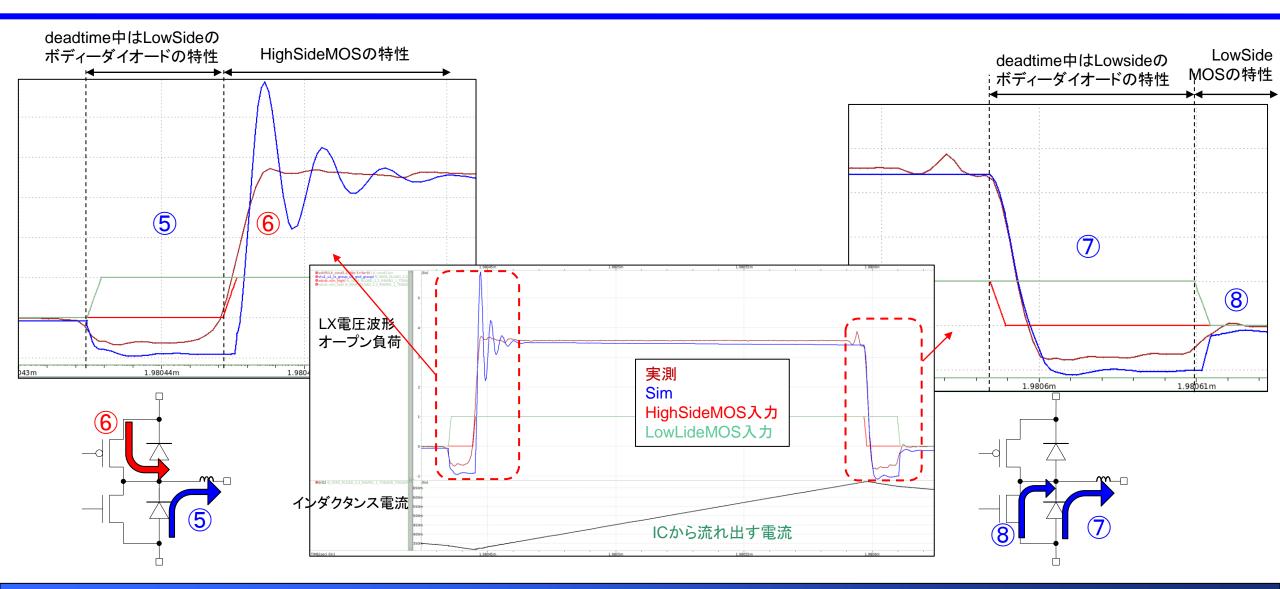

# マクロモデルを用いた考察(オープン負荷)

# マクロモデルを用いた考察(2.2Ω負荷)

- 背景と目的

- 実測によるDCDCコンバータのインピーダンスモデル作成

- 実測環境と実測結果

- シミュレーション結果と実測比較

- 実測との誤差が大きい原因検討

- IBISモデルからSpiceマクロモデル生成

- Spiceマクロモデル改良

- ・まとめ

- 今後の課題と活動内容

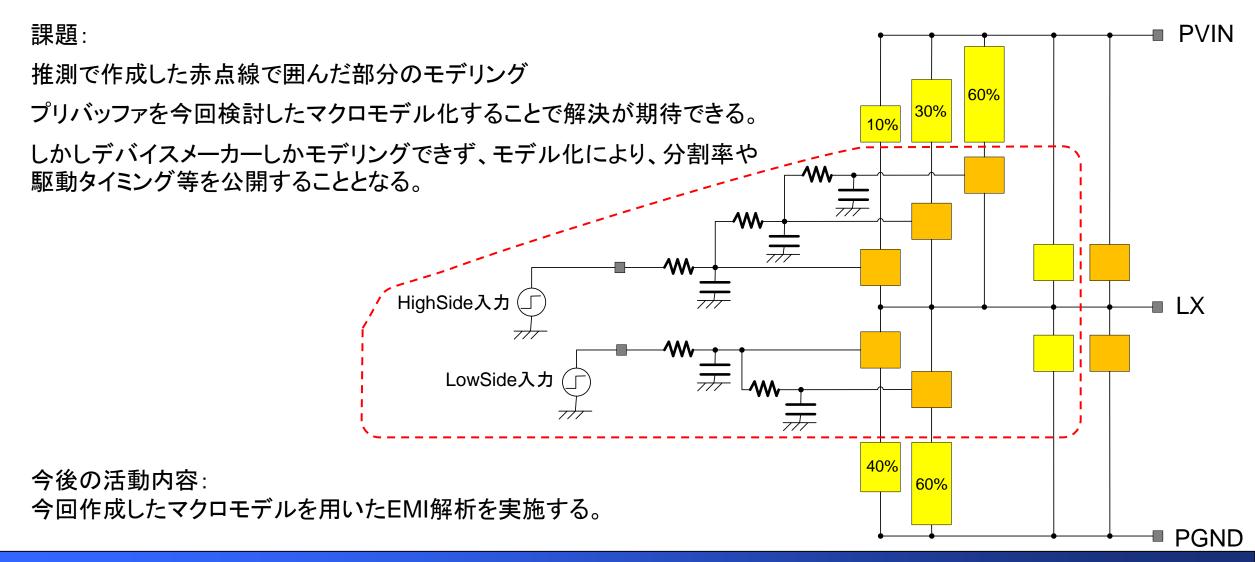

# Spiceマクロモデル改良

デバイス設計者様に確認したところドライバは

·HighSide:小·中·大

·LowSide:中·大

に分け適切に駆動していることが判明。

駆動力の内訳情報がないが、電流駆動力を

HighSide: 10%,30%,60%

LowSide: 40%,60%

のモデルに分割試行

60% 10% HighSide入力 ⊸LX LowSide入力 40% \_ PGND

改良Spiceマクロモデル

駆動力毎にGelementを分割し、RCラダーで遅延を生成

デバイスを分割し、各デバイスの動作タイミングをシフトすることで電流集中を緩和する。

**PVIN**

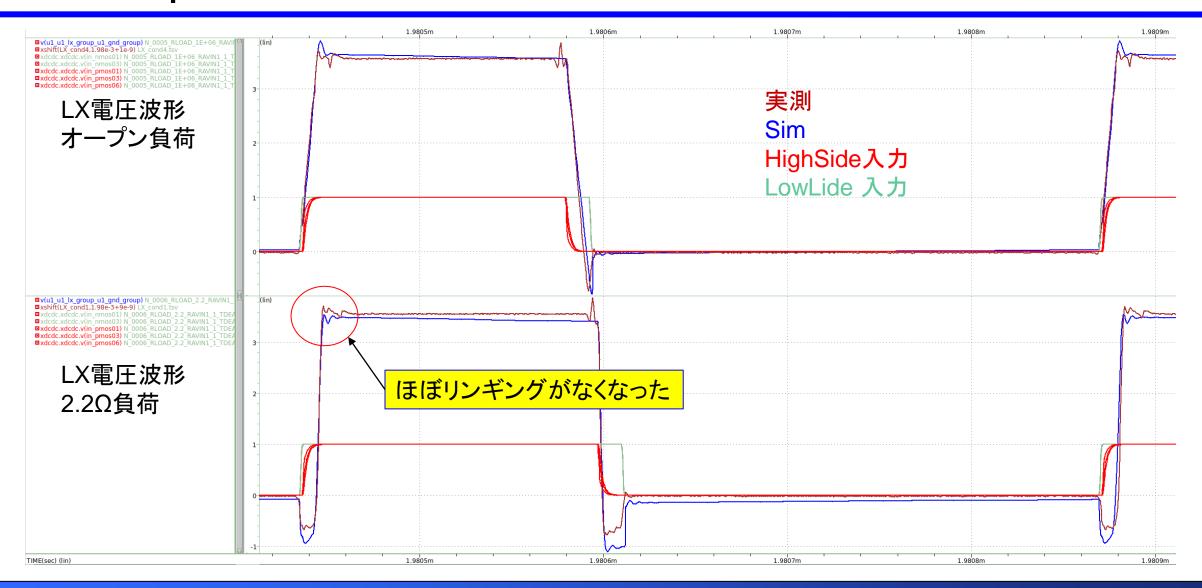

# 改良SpiceマクロモデルのSim結果(シンプル実装モデル)

- 背景と目的

- 実測によるDCDCコンバータのインピーダンスモデル作成

- 実測環境と実測結果

- シミュレーション結果と実測比較

- 実測との誤差が大きい原因検討

- IBISモデルからSpiceマクロモデル生成

- Spiceマクロモデル改良

- まとめ

- 今後の課題と活動内容

#### まとめ

- 今回の検討で、出力波形を合わせるためには、デバイス内の駆動ドライバ構成およびその駆動タイミングが重要であることを確認した。

- デバイスを分割し、電流集中を抑制することで課題であったリンギングをなくすことができた。

# 今後の課題および活動内容