### JEITA 第14回LPBフォーラム

# 標準化をめざしたDCDC電源回路のビヘイビアモデルの検討

モデルベースデザイン/システム設計WG 電源設計TG 坂田和之

- 背景と目的

- 測定環境と実測結果

- デバイスモデルのインピーダンス確認

- ・ 実装モデル概要説明

- シミュレーションと実測比較:IBISモデル

- SPICEマクロモデル検討

- シミュレーションと実測比較:SPICEマクロモデル

- まとめと課題

## 背景と目的

パワーデバイスモデルの多くは、特定の回路シミュレータ用Spiceモデルで提供

→回路シミュレータに制限がある

パワーデイバスモデルをIBIS等のビヘイビアモデルで実現できれば

→回路シミュレータの制限がなくなり、利便性が向上

さらに、実測からIBIS等のビヘイビアモデルを作成できれば

→モデル作成が容易になる。

・電源設計TGでは、パワーデバイスの1つであるDCDCコンバータをIBIS化し、簡易ビヘイビアモデルのEMIシミュレーションへの適用可能性を検討しています。

- 背景と目的

- 測定環境と実測結果

- デバイスモデルのインピーダンス確認

- 実装モデル概要説明

- シミュレーションと実測比較:IBISモデル

- SPICEマクロモデル検討

- シミュレーションと実測比較:SPICEマクロモデル

- まとめと課題

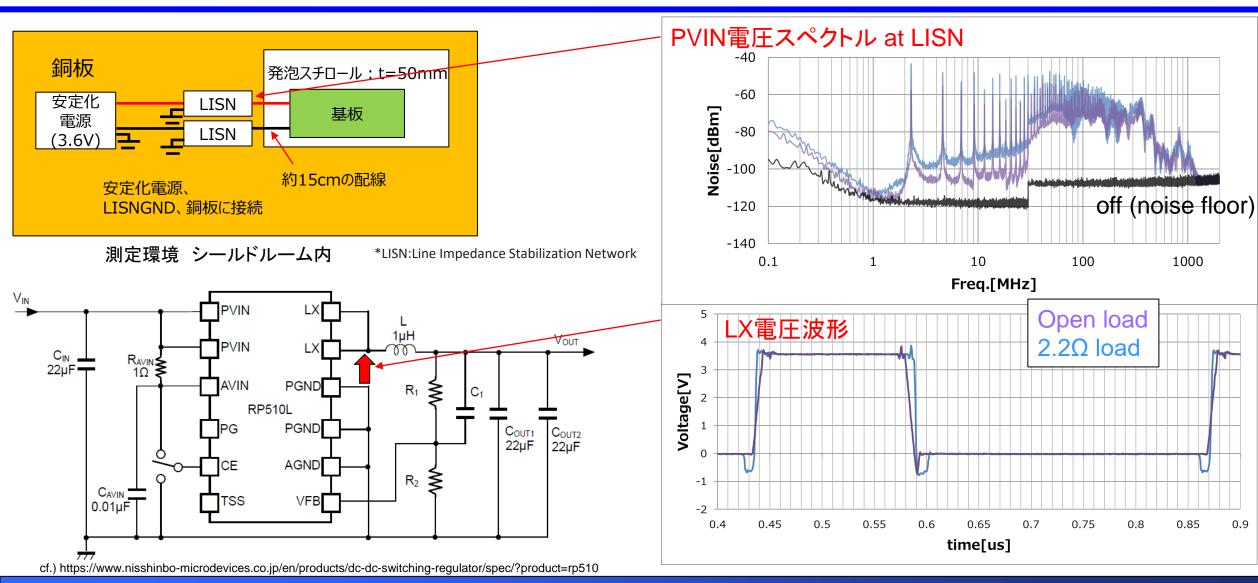

# 測定環境と実測結果

- ・ 背景と目的

- 測定環境と実測結果

- デバイスモデルのインピーダンス確認

- 実装モデル概要説明

- シミュレーションと実測比較:IBISモデル

- SPICEマクロモデル検討

- シミュレーションと実測比較:SPICEマクロモデル

- まとめと課題

# デバイスモデルのインピーダンス確認

高精度EMIシミュレーションには、 デバイスのインピーダンスを正しくモデリングすることは必須。 デバイスを実測し、モデルに含まれる容量を確認する。

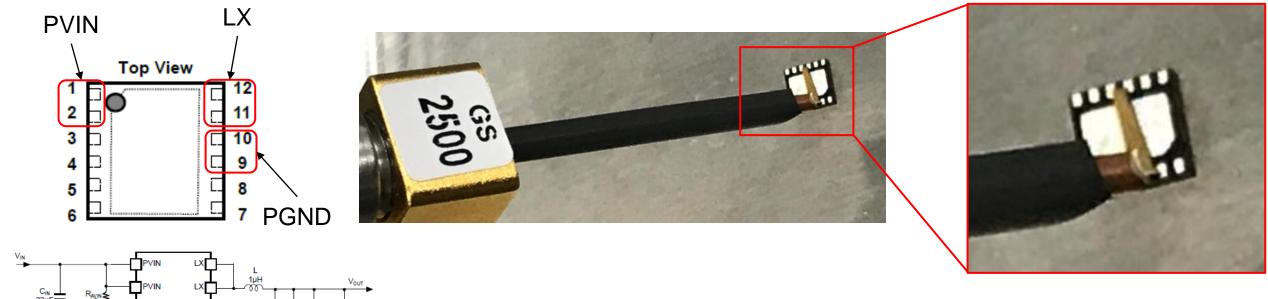

# DCDC コンバータのインピーダンス測定

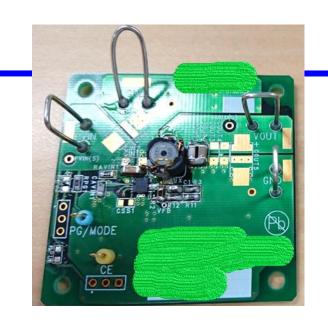

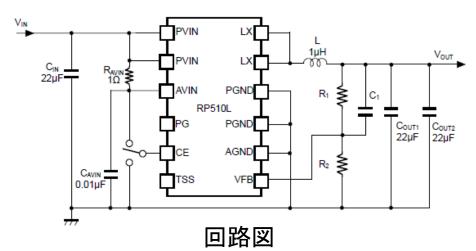

DCDC converter: RICOH RP510L004N-TR-A

#### IO Pins for impedance measurement

| Pin(S-G)  | No.(S-G)    | Pitch(mm)    | Bias voltage(V)             | Freq.(Hz)※ |

|-----------|-------------|--------------|-----------------------------|------------|

| PVIN-PGND | PIN2-PIN10  | 2.65mm±0.3mm | 0,0.3,0.6,1,2,3,3.6,4,5,5.5 | 1k-3G      |

| PVIN-LX   | PIN2-PIN11  | 2.6mm±0.3mm  | 0,0.3,0.6,1,2,3,3.6,4,5,5.5 | 1k-3G      |

| LX-PGND   | PIN11-PIN10 | 0.5mm±0.1mm  | 0,0.3,0.6,1,2,3,3.6,4,5,5.5 | 1k-3G      |

本報告での使用装置:HP4291A

cf.) https://www.nisshinbo-microdevices.co.jp/en/products/dc-dc-switching-regulator/spec/?product=rp510

**Typical Application Circuit**

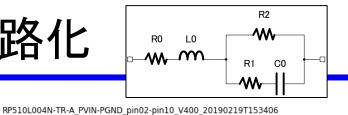

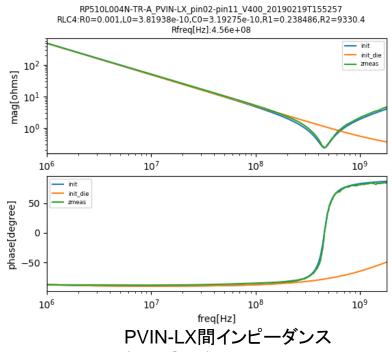

# インピーダンス実測と等価回路化

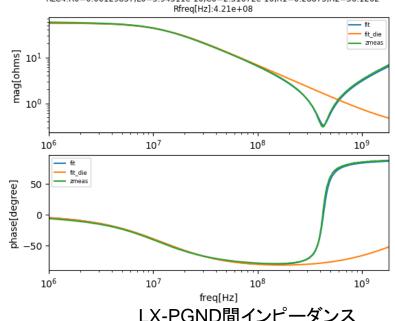

RLC4:R0=0.00129837,L0=5.94311e-10,C0=2.31672e-10,R1=0.28875,R2=56.1262 Rfreq[Hz]:4.21e+08

RP510L004N-TR-A\_2\_LX-PGND\_pin11-pin10\_V500\_20190219T165129

- fit\_die \_\_\_\_ zmeas [smho]gem 10<sub>1</sub> 10<sup>0</sup> 10<sup>6</sup>  $10^{7}$ 108 10<sup>9</sup> 50 phase[degree]

10<sup>7</sup>

10<sup>6</sup>

RLC4:R0=0.663538,L0=1.86253e-10,C0=1.85708e-10,R1=0.00560028,R2=1.87806e+07

Rfreq[Hz]:8.17e+08

(HighSide)

LX-PGND間インピーダンス (LowSide)

PVIN-PGND間インピーダンス

freq[Hz]

108

|           | L(nH) | C(pF) | R(Ω) | Rleak(Ω) |

|-----------|-------|-------|------|----------|

| PVIN-PGND | 0.19  | 186   | 0.66 | 1.87e7   |

| PVIN-LX   | 0.38  | 319   | 0.24 | 9339     |

| LX-PGND   | 0.59  | 232   | 0.29 | 56.12    |

RCはこの値を採用 LはLX,PVIN,PGND共通で1.5nH とした

10<sup>9</sup>

### IBISファイル中の容量記述

実測した容量をIBIS内のC\_comp\_pullup、C\_comp\_pulldownに記載

今回はリコー電子デバイス様のモデリング精度が高く、容量がほぼ一致しているので問題ないが、 大きくずれていた場合はspiceネットに容量を追加してIBISを作成しなおす必要がある。

- 背景と目的

- 測定環境と実測結果

- デバイスモデルのインピーダンス確認

- ・ 実装モデル概要説明

- シミュレーションと実測比較:IBISモデル

- SPICEマクロモデル検討

- シミュレーションと実測比較:SPICEマクロモデル

- まとめと課題

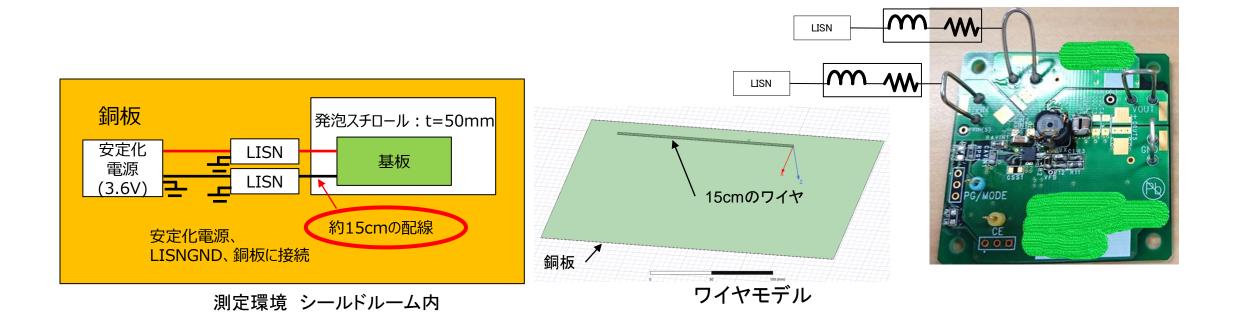

# 実装モデル

cf.) https://www.nisshinbo-microdevices.co.jp/en/products/dc-dc-switching-regulator/spec/?product=rp510

電源・グランド接続ポートは5cm下の金属プレートを基準にポート作成

## LISNから基板までのワイヤ

LISNから基板までの15cmのワイヤは約15nHのインダクタンスを持ち、100MHz以上では9.4Ω以上となる。 スペアナの50Ω終端インピーンスに対して無視できない大きさのためモデル化

- 背景と目的

- 測定環境と実測結果

- デバイスモデルのインピーダンス確認

- ・ 実装モデル概要説明

- シミュレーションと実測比較:IBISモデル

- SPICEマクロモデル検討

- シミュレーションと実測比較:SPICEマクロモデル

- まとめと課題

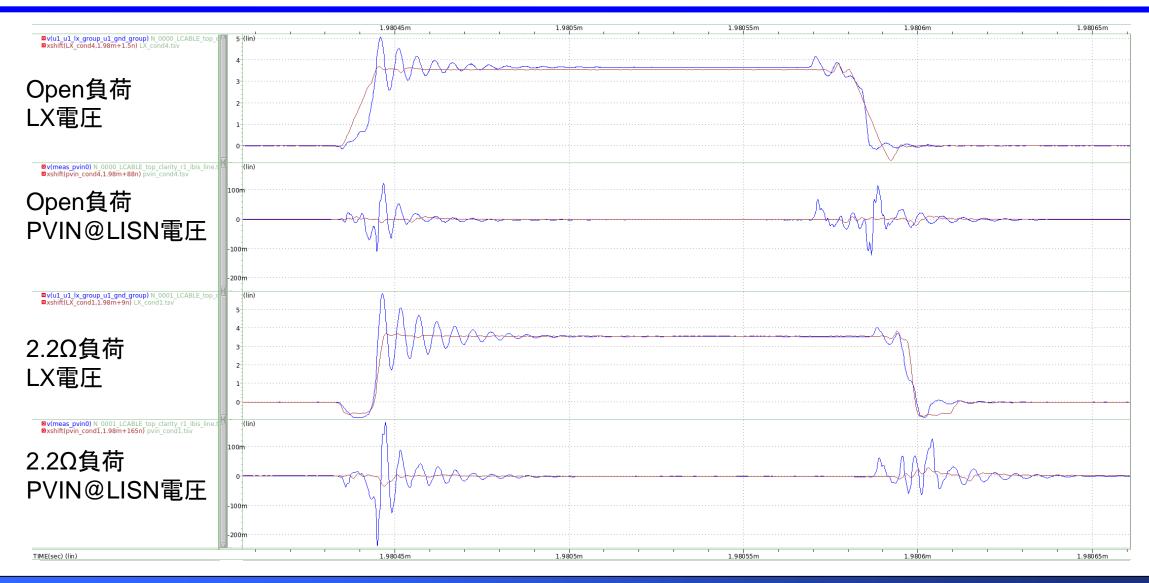

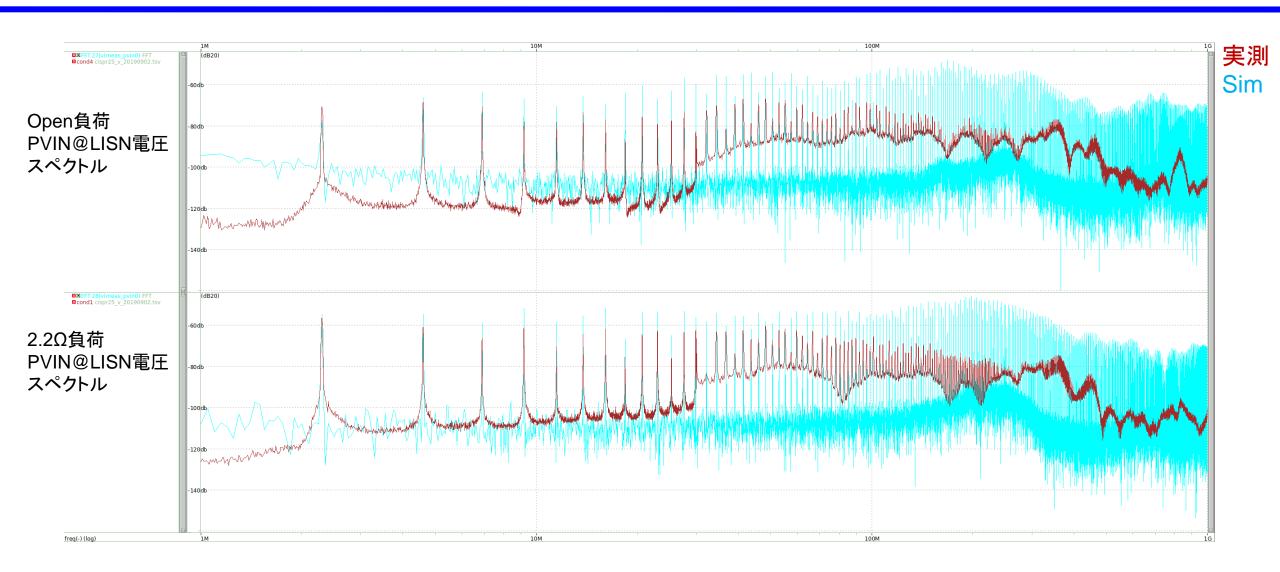

# Sim (with IBIS) vs 実測:電圧波形

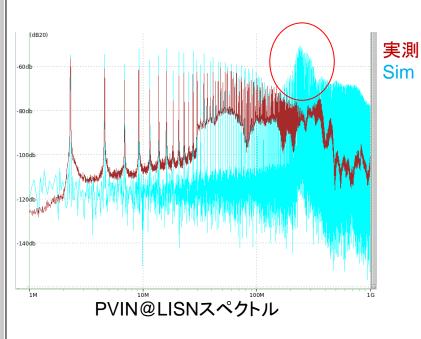

### Sim (with IBIS) vs 実測: PVIN @ LISN電圧スペクトル

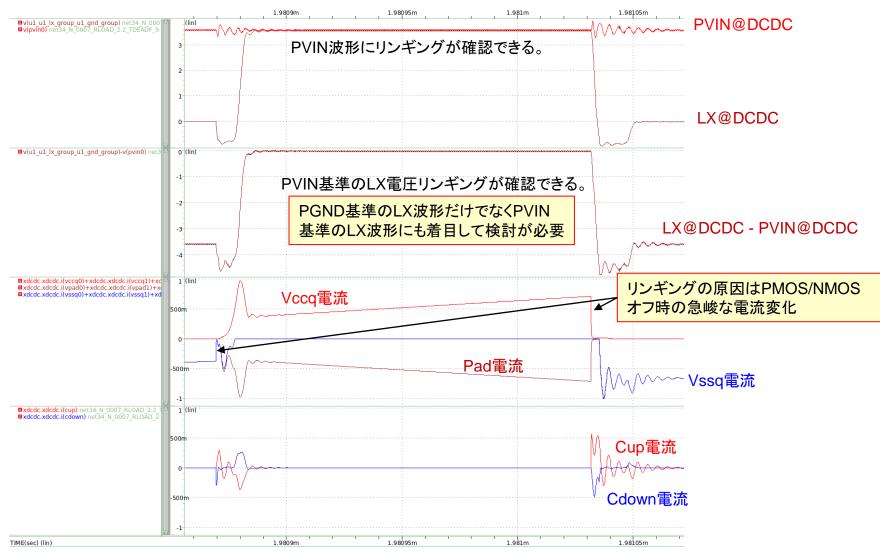

# 考察:リンギングの原因検討

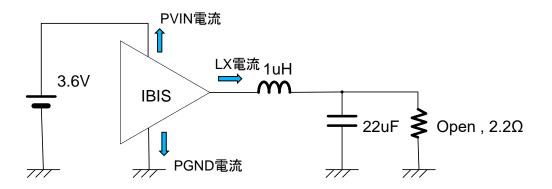

#### 基本回路トポロジにおける

#### デバイス単体動作時の電流を確認

# 考察: 電流変化の緩和について

Simモデルは実物に比べて、電流変化が大きいと推測 電流変化を緩和する方法を検討

IBISモデルのままでは、回路シミュレータでの取り扱いが不明確なため検討が難しい

Spiceマクロモデルにて電流緩和を検討

- 背景と目的

- 測定環境と実測結果

- デバイスモデルのインピーダンス確認

- ・ 実装モデル概要説明

- シミュレーションと実測比較:IBISモデル

- SPICEマクロモデル検討

- シミュレーションと実測比較:SPICEマクロモデル

- まとめと課題

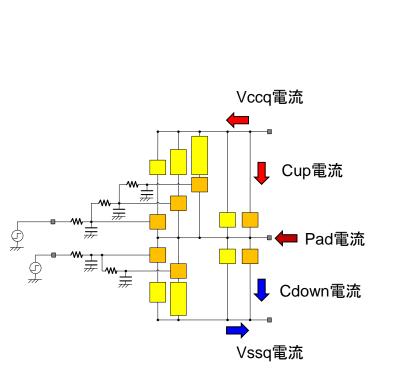

# Spiceマクロモデル

デバイス設計者様に確認したところドライバは

·HighSide:小·中·大

·LowSide:中·大

に分け適切に駆動しているとのこと。

駆動力の内訳情報は秘密のため、電流駆動力を

HighSide: 10%,30%,60%

LowSide: 40%,60%

のモデルに分割試行

10% PC HighSide入力() ⊸LX GC LowSide入力 PC:Power Clamp GC:GND Clamp 40% RC:抵抗·容量直列 60% デバイスを分割し、各デバイスの動作タイミング \_ PGND をシフトすることで電流集中を緩和する。

60%

Spiceマクロモデル

駆動力毎にGelementを分割し、RCラダーで遅延を生成

**■PVIN**

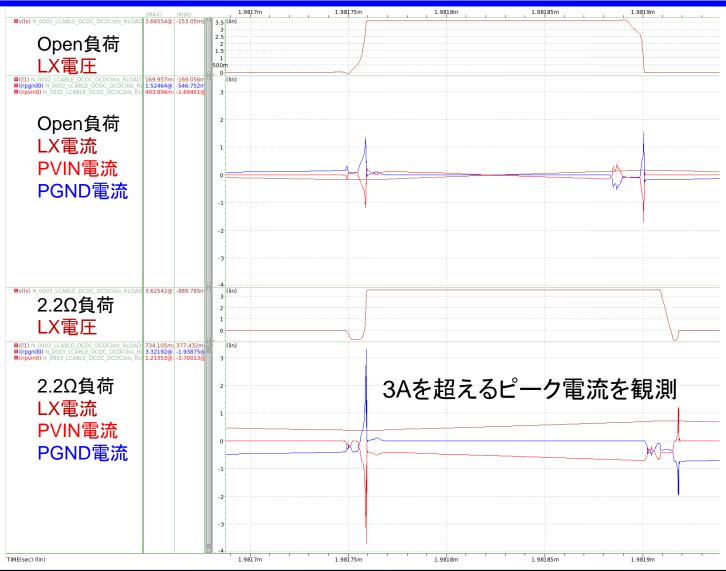

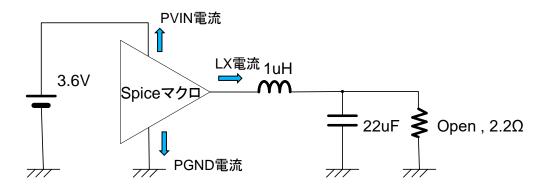

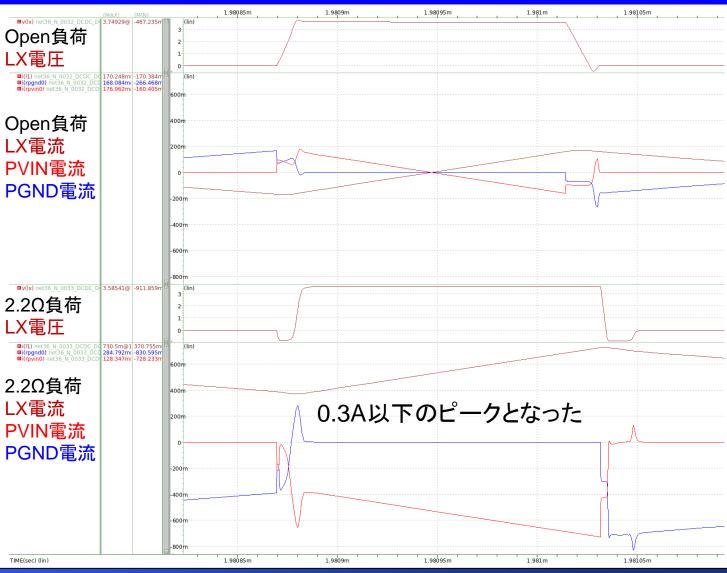

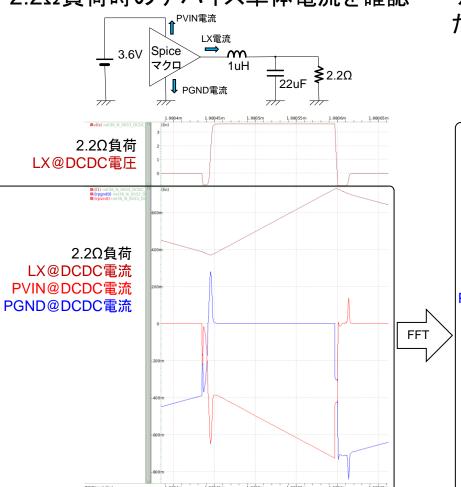

# Spiceマクロモデルのデバイス単体電流

基本回路トポロジにおけるデバイス単体動作時 の電流を確認

- 背景と目的

- 測定環境と実測結果

- デバイスモデルのインピーダンス確認

- ・ 実装モデル概要説明

- シミュレーションと実測比較:IBISモデル

- SPICEマクロモデル検討

- シミュレーションと実測比較:SPICEマクロモデル

- まとめと課題

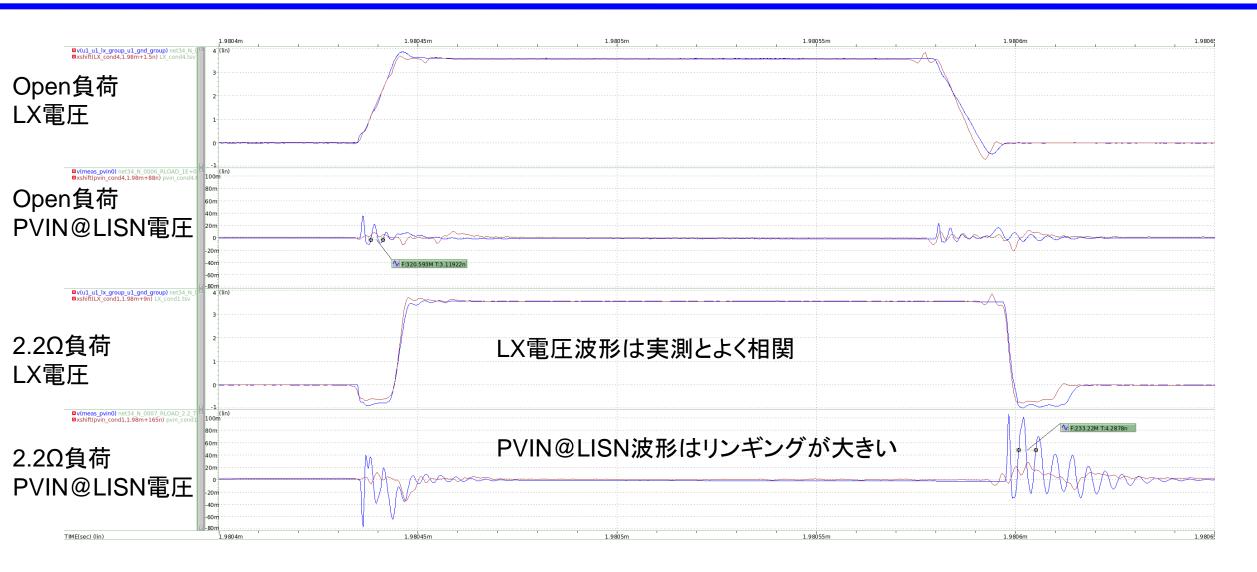

# Sim (with Spiceマクロモデル) vs 実測:電圧波形

# 考察:2.2Ω負荷でリンギングが大きい原因検討

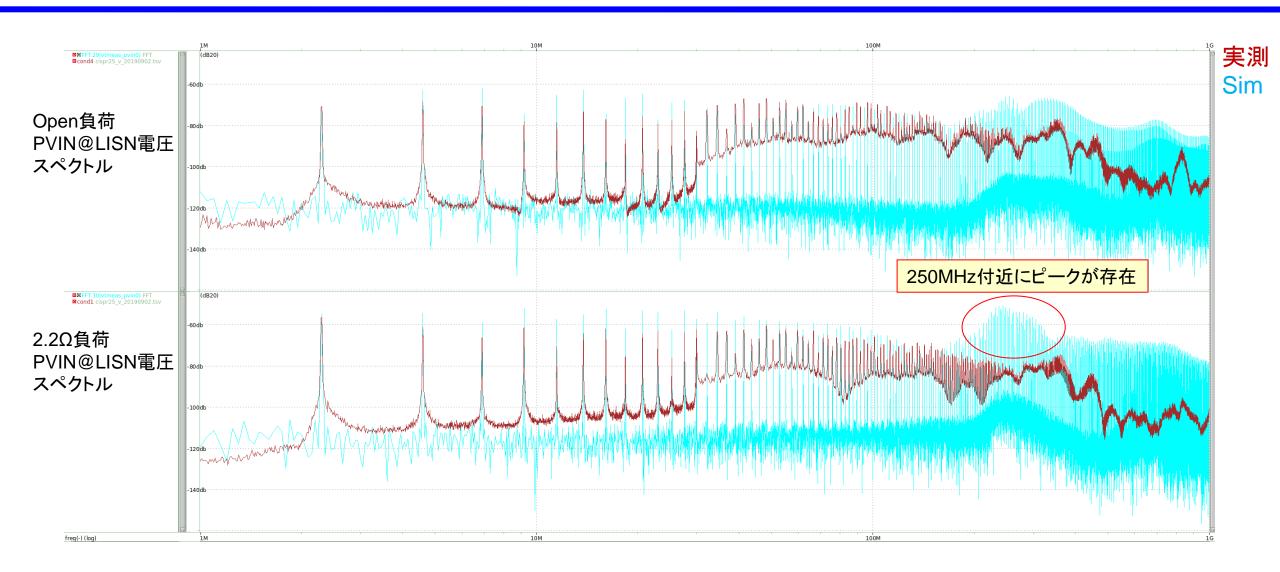

### Sim (with Spiceマクロモデル) vs 実測: PVIN@LISN電圧スペクトル

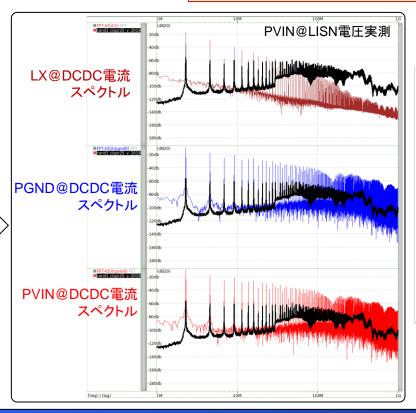

## 考察: 2.2Ω負荷時の250MHz付近のピーク原因検討

2.2Ω負荷時のデバイス単体電流を確認

デバイス単体電流スペクトルと実測において、250MHz付近のピークは目立たないが、SimのPVIN@LISNには大きなピークが存在する。

実装モデルの妥当性確認が必要 (特にパッケージインダクタンス)

- 背景と目的

- 測定環境と実測結果

- デバイスモデルのインピーダンス確認

- 実装モデル概要説明

- シミュレーションと実測比較:IBISモデル

- SPICEマクロモデル検討

- シミュレーションと実測比較:SPICEマクロモデル

- まとめと課題

## まとめと課題

#### まとめ

- SPICEマクロモデルを作成し、電流変化を緩和することでGND基準の出力電圧 波形は実測とよく一致するようになった。

- PMOS/NMOSがオフするときにPVIN波形にリンギングが発生している。

- 実装系のインピーダンスが実物とずれている可能性がある。

#### 課題

- 電流変化の妥当性

- パッケージインダクタンスの妥当性

# 終わり

# プログラム

|   | 時間          | 内容                                                                                                |

|---|-------------|---------------------------------------------------------------------------------------------------|

| 1 | 14:00-14:10 | <b>開催にあたって</b> JEITA SD-TC 委員長 東芝デバイス&ストレージ(株) 福場 義憲                                              |

| 2 | 14:10-14:30 | IEEE2401-2019の改訂に向けた検討状況報告<br>富士通(株)<br>大塚 育生                                                     |

| 3 | 14:30-14:50 | SerDesのイミュニティーモデルとその活用<br>コニカミノルタ(株)<br>野村 毅                                                      |

| 4 | 14:50-15:10 | <b>標準化をめざしたDCDC電源回路のビヘイビアモデルの検討</b> ルネサスエレクトロニクス(株) 坂田 和之                                         |

|   | 15:10-15:20 | 休憩                                                                                                |

| 5 | 15:20-17:00 | 【招待講演+ディスカッション】<br>超高速インターフェースの信号解析技術に求められる<br>インターコネクトモデルとは?<br>ファシリテータ シーメンスEDAジャパン(株)<br>眞篠 国素 |