жңҖиҝ‘гҒ®гҒҠзҹҘгӮүгҒӣ

- 2026-4-2

-

第134еҸ· LPBгғӢгғҘгғјгӮ№пјҲLPBгӮ·гӮ№гғҶгғ гӮҪгғӘгғҘгғјгӮ·гғ§гғігғ•гӮ©гғјгғ©гғ иіҮж–ҷжҺІијү)

- 2026-3-5

-

第133еҸ· LPBгғӢгғҘгғјгӮ№(гҖҢLPBгӮҪгғӘгғҘгғјгӮ·гғ§гғігғ•гӮ©гғјгғ©гғ гҖҚгҒ„гӮҲгҒ„гӮҲжҳҺж—Ҙ!)

- 2026-2-24

-

第132еҸ· LPBгғӢгғҘгғјгӮ№(гҖҢLPBгӮҪгғӘгғҘгғјгӮ·гғ§гғігғ•гӮ©гғјгғ©гғ гҖҚжқҘйҖұй–ӢеӮ¬пјҒ)

About Us

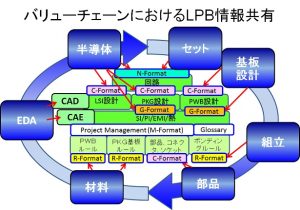

JEITA еҚҠе°ҺдҪ“пјҶгӮ·гӮ№гғҶгғ й–ӢзҷәжҠҖиЎ“гӮөгғ–гӮігғҹгғғгғҶгӮЈгҒҜгҖҒгҖҢеҚҠе°ҺдҪ“гҖҚгҒЁгҖҢгӮ·гӮ№гғҶгғ гҖҚгҒ®иЁӯиЁҲжҠҖиЎ“гҒ®иһҚеҗҲпјҲеҚ”иӘҝиЁӯиЁҲпјүгӮ’зӣ®жҢҮгҒ—гҒҰжҙ»еӢ•гҒ—гҒҰгҒ„гҒҫгҒҷгҖӮ

йӣ»еӯҗж©ҹеҷЁгҒ®й–Ӣзҷәгғ»иІ©еЈІгҒ®ж°ҙе№іеҲҶжҘӯгҒҢйҖІгӮҖдёӯгҖҒ競дәүеҠӣгҒҢгҒӮгӮӢиЈҪе“ҒгӮ’еёӮе ҙжҠ•е…ҘгҒҷгӮӢгҒ«гҒҜгӮөгғ—гғ©гӮӨгғҒгӮ§гғјгғігҒ®дёӯгҒ«ж•ЈеңЁгҒҷгӮӢжҠҖиЎ“гӮ’гӮҝгӮӨгғ гғӘгғјгҒ«иһҚеҗҲгҒ—гҖҒе•Ҷе“ҒдјҒз”»гӮ’з·ҙгӮӢгҒ“гҒЁгҒҢдёҚеҸҜж¬ гҒ§гҒҷгҖӮгҒқгҒ®зӮәгҒ«гҒҜеҖӢгҖ…гҒ®жҠҖиЎ“гҒ®жөҒйҖҡжҖ§гҒҢйҮҚиҰҒгҒЁгҒӘгӮҠгҒҫгҒҷгҖӮжҲ‘гҖ…гҒҢдјҒз”»гҒ—гҒҹLSIгғ»гғ‘гғғгӮұгғјгӮёгғ»гғңгғјгғүпјҲLPB)зӣёдә’иЁӯиЁҲиҰҸж јIEC 63055/IEEE2401-2019гҒҜгҖҒгҒ“гӮҢгӮ’жӢ…гҒҶгҒҹгӮҒгҒ®еӣҪйҡӣжЁҷжә–гҒ§гҒҷгҖӮеҚҠе°ҺдҪ“пјҶгӮ·гӮ№гғҶгғ й–ӢзҷәжҠҖиЎ“гӮөгғ–гӮігғҹгғғгғҶгӮЈгҒҜгҖҒгҒ“гҒ®жЁҷжә–гӮ’гғҷгғјгӮ№гҒ«гҖҢеҚҠе°ҺдҪ“гӮ’гӮ·гӮ№гғҶгғ иЁӯиЁҲгҒ«з”ҹгҒӢгҒҷгҖҚгҖҢгӮ·гӮ№гғҶгғ гҒ®иҰҒжұӮгғ»еҲ¶зҙ„гӮ’еҚҠе°ҺдҪ“гҒ«еҸ–гӮҠиҫјгӮҖгҖҚеҸҢж–№еҗ‘гҒ®иЁӯиЁҲжҠҖиЎ“гҒ®ж•ҙеӮҷгӮ’зӣ®жҢҮгҒ—з ”з©¶гғ»й–ӢзҷәгӮ’иЎҢгҒЈгҒҰгҒ„гҒҫгҒҷгҖӮгҒ“гҒ®жҙ»еӢ•гӮ’йҖҡгҒҳгҒҰеҚҠе°ҺдҪ“з”ЈжҘӯгҒҠгӮҲгҒійӣ»еӯҗж©ҹеҷЁжҘӯз•ҢгҒ®зҷәеұ•гҒ«еҜ„дёҺгҒ—гҒҰиЎҢгҒҚгҒҫгҒҷгҖӮ

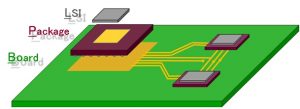

What is LPB ?

LPBгҒЁгҒҜLSIгғ»гғ‘гғғгӮұгғјгӮёгғ»гғңгғјгғүгҒ®зӣёдә’иЁӯиЁҲгҒ®гҒ“гҒЁгҒ§гҒҷгҖӮLPBгҒҢйҖЈжҗәгҒ—еҗҲгҒЈгҒҰ競дәүеҠӣгҒӮгӮӢиЈҪе“ҒиЁӯиЁҲгӮ’иҝ…йҖҹгҒ«д»•дёҠгҒ’гӮӢгҒ“гҒЁгӮ’зӣ®жҢҮгҒ—гҒҫгҒҷгҖӮ(more)>>

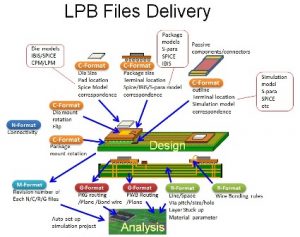

IEC 63055/IEEE2401-2019

LPBгҒ«й–ўгӮҸгӮӢиЁӯиЁҲгҒ«еҝ…иҰҒгҒӘжғ…е ұгӮ„иЁӯиЁҲзөҗжһңгӮ’жөҒйҖҡгҒ•гҒӣгӮӢзӮәгҒ«жҲ‘гҖ…гҒҢжҺЁйҖІгҒ—гҒҰгҒ„гӮӢеӣҪйҡӣжЁҷжә–иҰҸж јгҒ§гҒҷпјҲиіје…ҘгҒҜгҒ“гҒЎгӮүгҒӢгӮүпјүгҖӮгӮөгғігғ—гғ«гғ•гӮЎгӮӨгғ«гҒҜгҖҒгҒ“гҒЎгӮүгҒӢгӮүгғҖгӮҰгғігғӯгғјгғүгҒ§гҒҚгҒҫгҒҷгҖӮ(more)>>

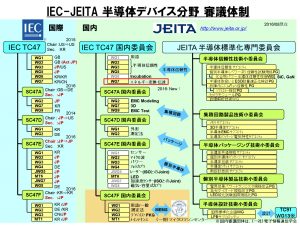

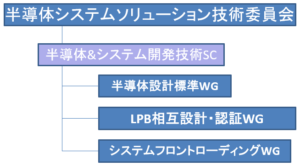

Organization

жҲ‘гҖ…гҒ®зӣ®зҡ„е®ҹзҸҫгҒ®зӮәгҒ«гҖҒLPBй–“гҒ®иЁӯиЁҲгӮӨгғігӮҝгғјгғ•гӮ§гғјгӮ№гҒ®й–ӢзҷәгҖҒгғўгғҮгғ«гғҷгғјгӮ№гғҮгӮ¶гӮӨгғіжҠҖиЎ“гҒ®й–ӢзҷәгҖҒгҒқгӮҢгӮүгӮ’еӣҪйҡӣжЁҷжә–еҢ–гҒҷгӮӢйғЁй–ҖгӮ’иЁӯзҪ®гҒ—гҒҰгҒ„гҒҫгҒҷгҖӮ(more)>>

еҚҠе°ҺдҪ“жЁҷжә–гғҜгғјгӮӯгғігӮ°гӮ°гғ«гғјгғ—

еҚҠе°ҺдҪ“жЁҷжә–гғҜгғјгӮӯгғігӮ°гӮ°гғ«гғјгғ—гҒҜгҖҒеӣҪйҡӣжЁҷжә–иҰҸж јгҒ«дҝӮгӮӢиЁҲз”»гғ»з«ӢжЎҲгҒЁгҖҒе°Ҹ委員дјҡгҒ®гӮ№гғҶгӮўгғӘгғігӮ°гӮ’иЎҢгҒЈгҒҰгҒ„гҒҫгҒҷгҖӮ(more)>>

LPBзӣёдә’иЁӯиЁҲгғ»иӘҚиЁјгғҜгғјгӮӯгғігӮ°гӮ°гғ«гғјгғ—

LPBзӣёдә’иЁӯиЁҲгғ»иӘҚиЁјгғҜгғјгӮӯгғігӮ°гӮ°гғ«гғјгғ—гҒҜгҖҒIEC 63055/IEEE2401-2019гҒ®й–ӢзҷәгҒЁжҷ®еҸҠгӮ’иЎҢгҒЈгҒҰгҒ„гҒҫгҒҷгҖӮ(more)>>

гӮ·гӮ№гғҶгғ гғ•гғӯгғігғҲгғӯгғјгғҮгӮЈгғігӮ°гғҜгғјгӮӯгғігӮ°гӮ°гғ«гғјгғ—

гӮ·гӮ№гғҶгғ гғ•гғӯгғігғҲгғӯгғјгғҮгӮЈгғігӮ°гҒҜLPBгҒ«гҒҠгҒ‘гӮӢгӮ·гғҹгғҘгғ¬гғјгӮ·гғ§гғігҒҠгӮҲгҒігғўгғҮгғ«гғҷгғјгӮ№гғҮгӮ¶гӮӨгғіжҠҖиЎ“гҒ®з ”究й–ӢзҷәгӮ’иЎҢгҒЈгҒҰгҒ„гҒҫгҒҷгҖӮ (more)>>