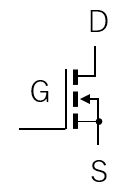

今回は東芝のMOS-FET(TPHR7904PB)を例にしてC-Formatを見ていきます。今回取り扱うMOS-FETは前回までのコンデンサや水晶振動子と異なり複雑な形状の端子を持っています。この部品のパッケージ種別はSOPとなります。

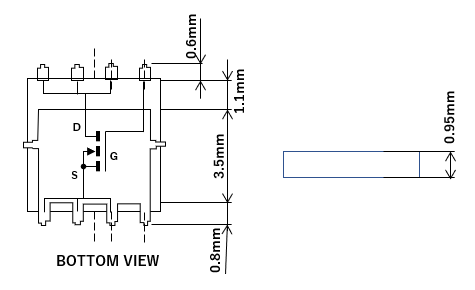

下図にこのMOS-FETのパッケージ構造を示します。

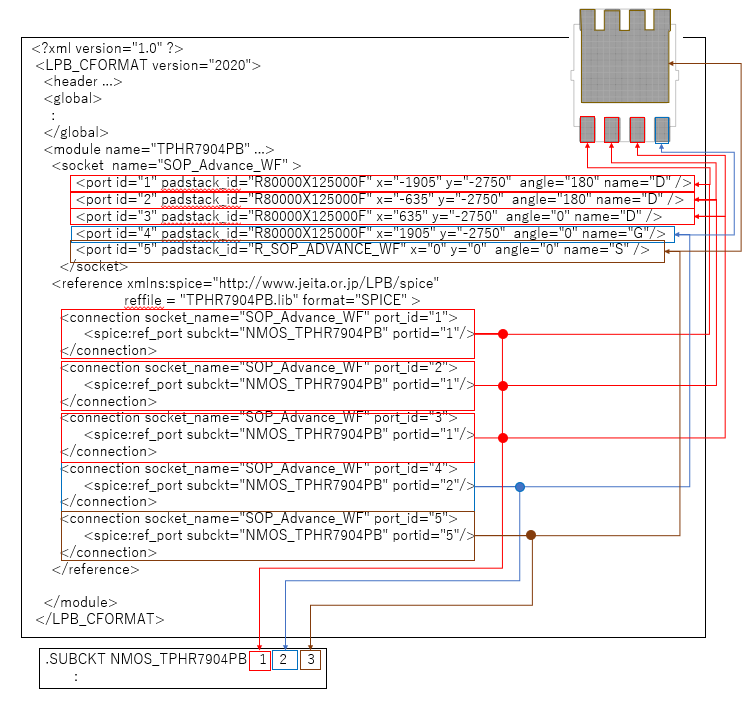

下にTPHR7904PBのC-Formatの例を示します。以後、このC-Formatの詳細を見ていきます。 他の例と同様に、このC-Formatもトップ要素の下に <header>, <global>, <module>の3つの要素を配置しています。

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 |

degree" /> </unit> <shape> <polygon id="COMP_SHAPE_SOP_Advance_WF" points="-2305,-3375,-2305,-2600,-2600,-2600,-2600,-250,-2750,-250, -2750,250,-2600,250,-2600,2600,-2305,2600,-2305,3375, 2305,3375,2305,2600,2600,2600,2600,250,2750,250,2750, -250,2600,-250,2600,-2600,2305,-2600,2305,-3375,-2305,-3375" /> <polygon id="PAD_SHAPE_r80000x125000" points="325,625,362,615,390,587,400,550,400,-550,390,-588,362, -615,325,-625,-325,-625,-363,-615, -390,-588,-400,-550, -400,550,-390,587,-363,615,-325,625,325,625" /> <polygon id="PAD_SHAPE_r_sop_advance_wf" points="-2150,-1400,-2187,-1390,-2215,-1362,-2225,-1325,-2225,2225, -2235,2263,-2262,2290,-2300,2300,-2230,2300,-2267,2310,-2295, 2338,-2305,2375,-2305,3300,-2295,3338,-2267,3365,-2230,3375, -1580,3375,-1542,3365,-1515,3338,-1505,3300,-1505,2375,-1495, 2338,-1467,2310,-1430,2300,-1110,2300,-1072,2310,-1045,2338, -1035,2375,-1035,3300,-1025,3338,-997,3365,-960,3375,-310,3375, -272,3365,-245,3338,-235,3300,-235,2375,-225,2338,-197,2310, -160,2300,160,2300,198,2310,225,2338,235,2375,235,3300,245, 3338,273,3365,310,3375,960,3375,998,3365,1025,3338,1035,3300, 1035,2375,1045,2338,1073,2310,1110,2300,1430,2300,1468,2310, 1495,2338,1505,2375,1505,3300,1515,3338,1543,3365,1580,3375, 2230,3375,2268,3365,2295,3338,2305,3300,2305,2375,2295,2338, 2268,2310,2230,2300,2300,2300,2263,2290,2235,2263,2225,2225,2225, -1325,2215,-1362,2188,-1390,2150,-1400,-2150,-1400" /> </shape> <padstack_def> <padstack id="R80000X125000F"> <ref_shape shape_id="PAD_SHAPE_r80000x125000" type="Land" x="0" y="0" angle="0" pad_layer="BOTTOM" /> </padstack> <padstack id="R_SOP_ADVANCE_WF"> <ref_shape shape_id="PAD_SHAPE_r_sop_advance_wf" type="Land" x="0" y="0" angle="0" pad_layer="BOTTOM" /> </padstack> </padstack_def> </global> <module name="TPHR7904PB" type="PKG" shape_id="COMP_SHAPE_SOP_Advance_WF" x="0" y="0" angle="0" thickness="0.95" > <socket name="SOP_Advance_WF" > <port id="1" padstack_id="R80000X125000F" x="-1905" y="-2750" angle="180" name="D" /> <port id="2" padstack_id="R80000X125000F" x="-635" y="-2750" angle="180" name="D" /> <port id="3" padstack_id="R80000X125000F" x="635" y="-2750" angle="0" name="D" /> <port id="4" padstack_id="R80000X125000F" x="1905" y="-2750" angle="0" name="G"/> <port id="5" padstack_id="R_SOP_ADVANCE_WF" x="0" y="0" angle="0" name="S" /> <portgroup name="drain> <mustjoin/> <ref_port id="1"/> <ref_port id="2"/> <ref_port id="3"/> </portgroup> </socket> <reference xmlns:spice="http://www.jeita.or.jp/LPB/spice" reffile = "TPHR7904PB.lib" format="SPICE" > <connection socket_name="SOP_Advance_WF" port_id="1"> <spice:ref_port subckt="NMOS_TPHR7904PB" portid="1"/> </connection> <connection socket_name="SOP_Advance_WF" port_id="2"> <spice:ref_port subckt="NMOS_TPHR7904PB" portid="1"/> </connection> <connection socket_name="SOP_Advance_WF" port_id="3"> <spice:ref_port subckt="NMOS_TPHR7904PB" portid="1"/> </connection> <connection socket_name="SOP_Advance_WF" port_id="4"> <spice:ref_port subckt="NMOS_TPHR7904PB" portid="2"/> </connection> <connection socket_name="SOP_Advance_WF" port_id="5"> <spice:ref_port subckt="NMOS_TPHR7904PB" portid="5"/> </connection> </reference> </module> </LPB_CFORMAT> |

C-Formatの構成

まず最初に前回までの復習を兼ねてC-Formatの構造を説明します。

C-Formatのトップ要素は<LPB_CFORMAT>です。トップ要素の下に<header>, <global>, <module>の3つの要素を配置します。

|

1 2 3 4 5 6 |

<?xml version="1.0" ?> <LPB_CFORMAT version="2020"> <header>要素 <global>要素 <module>要素 </LPB_CFORMAT> |

<header>要素

<header>要素にはproject 、design_revision 、company 、date の4つの属性を定義します。

|

1 2 |

<header company="TOSHIBA" project="Power MOSFET" date="20190621" design_revision ="1.0"/> |

<global>要素

このMOS-FETの<global>要素には他のサンプルと同様に以下の3つの要素が定義されています。

- <unit>要素

- <shape>要素

- <padstack_def>要素

<unit>要素

このサンプルのC-Formatでは長さ・座標の単位(ミリメートル)と角度の単位(degree、度)が定義されています。

|

1 2 3 4 |

<unit> <distance unit="um" /> <angle unit="degree" /> </unit> |

<angle>要素

<angle>は、C-Format内で使用する角度の単位を定義します。以下の2つを定義することができます。

angle : 度

radian : ラジアン

このサンプルでの角度は「度(degree)」で表現されまています。

<shape>要素

このサンプルでは、これまでに示したサンプルと違ってポリゴン(polygon)を使って形状を定義してます。またidも任意文字列で定義しています。

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 |

<shape> <polygon id="COMP_SHAPE_SOP_Advance_WF" points="-2305,-3375,-2305,-2600,-2600,-2600,-2600,-250,-2750,-250, -2750,250,-2600,250,-2600,2600,-2305,2600,-2305,3375, 2305,3375,2305,2600,2600,2600,2600,250,2750,250,2750, -250,2600,-250,2600,-2600,2305,-2600,2305,-3375,-2305,-3375" /> <polygon id="PAD_SHAPE_r80000x125000" points="325,625,362,615,390,587,400,550,400,-550,390,-588,362, -615,325,-625,-325,-625,-363,-615, -390,-588,-400,-550, -400,550,-390,587,-363,615,-325,625,325,625" /> <polygon id="PAD_SHAPE_r_sop_advance_wf" points="-2150,-1400,-2187,-1390,-2215,-1362,-2225,-1325,-2225,2225, -2235,2263,-2262,2290,-2300,2300,-2230,2300,-2267,2310,-2295, 2338,-2305,2375,-2305,3300,-2295,3338,-2267,3365,-2230,3375, -1580,3375,-1542,3365,-1515,3338,-1505,3300,-1505,2375,-1495, 2338,-1467,2310,-1430,2300,-1110,2300,-1072,2310,-1045,2338, -1035,2375,-1035,3300,-1025,3338,-997,3365,-960,3375,-310,3375, -272,3365,-245,3338,-235,3300,-235,2375,-225,2338,-197,2310, -160,2300,160,2300,198,2310,225,2338,235,2375,235,3300,245, 3338,273,3365,310,3375,960,3375,998,3365,1025,3338,1035,3300, 1035,2375,1045,2338,1073,2310,1110,2300,1430,2300,1468,2310, 1495,2338,1505,2375,1505,3300,1515,3338,1543,3365,1580,3375, 2230,3375,2268,3365,2295,3338,2305,3300,2305,2375,2295,2338, 2268,2310,2230,2300,2300,2300,2263,2290,2235,2263,2225,2225,2225, -1325,2215,-1362,2188,-1390,2150,-1400,-2150,-1400" /> </shape> |

<polygon> は閉じたポリゴン図形を定義する要素です。以下の必須属性を持ちます。

id

このshapeの識別子です。識別子はユニークである必要があります。

points

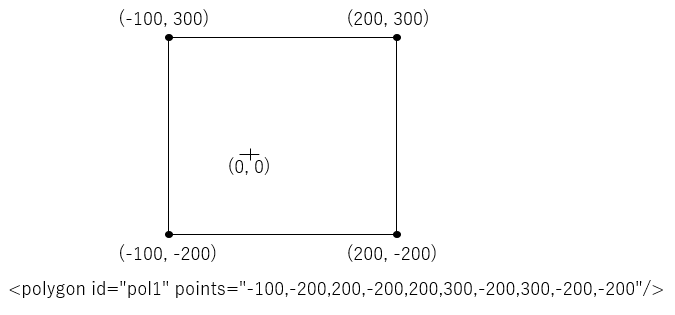

ポリゴン図形の頂点座標を定義します。"x座標, y座標, x座標, y座標, ...."と、座標を定義します。始点と終点の座標を同じとしてポリゴンを閉じます。例えば以下の例は左下点座標を(-100,-200)、右上点座標を(200,300)とする矩形となります。またポリゴン図形の原点は(0, 0)となります。

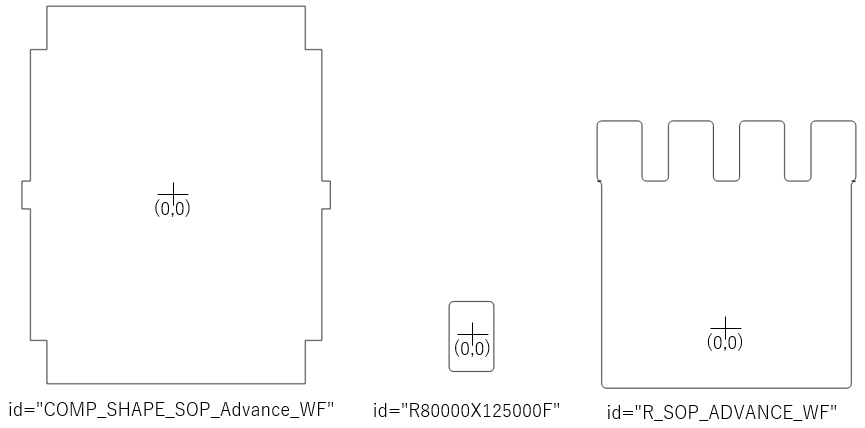

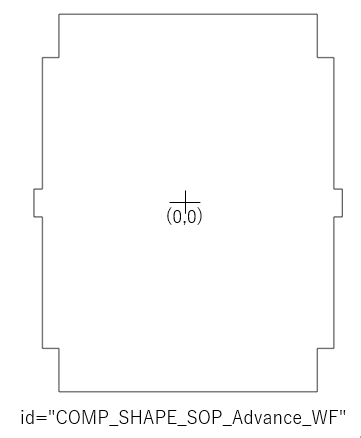

このサンプルのshapeで定義されているポリゴン図形はの下図の形状となります。

<padstack_def>要素

<padstack_def>要素では部品の電極(端子)を定義しています。

|

1 2 3 4 5 6 7 8 9 10 |

<padstack_def> <padstack id="R80000X125000F"> <ref_shape shape_id="PAD_SHAPE_r80000x125000" type="Land" x="0" y="0" angle="0" pad_layer="BOTTOM" /> </padstack> <padstack id="R_SOP_ADVANCE_WF"> <ref_shape shape_id="PAD_SHAPE_r_sop_advance_wf" type="Land" x="0" y="0" angle="0" pad_layer="BOTTOM" /> </padstack> </padstack_def> |

このサンプルでは、これまでの例と異なり<ref_shape>要素に'typeとangleの新しい2つの属性を使ってpadstackを定義しています。

|

1 2 3 4 |

<padstack id="R80000X125000F"> <ref_shape shape_id="PAD_SHAPE_r80000x125000" type="Land" x="0" y="0" angle="0" pad_layer="BOTTOM" /> </padstack> |

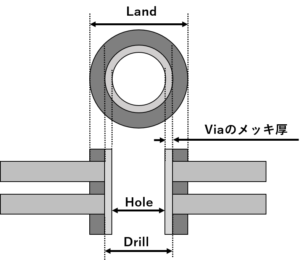

type

padstackは端子(電極)以外にもVIAの形状を定義するためにも使用します。VIAを定義する場合、金属箔の形状以外にドリル穴やクリアランス(antipad)の形を定義する必要があります。それらを区別するために type 属性に以下の値を設定します。

Land - ランド形状。いわゆる金属箔の形状です。(デフォルト値)

NonConnection - ネットとの接続をしないランド形状。

Antipad - ランドと異なるネットの導体パターンとのクリアランス用の形状です

Drill - VIAのドリル穴の形状です。

Hole - 穴の形状。Drillとの違いは :numref:via を参照ください。

SolderMask - ソルダマスクの形状です。

Resist - ソルダレジスト(メタルマスク)の形状です。いわゆるペーストはんだが塗布された形状です。

このサンプルの例では金属箔の形状を表す Land を明示的に設定しますが、省略しても同じ意味になります。

angle

shape_id で参照したshapeの回転角度を設定します。デフォルト値は0です。サンプルでの回転角度は0度なので、 angleを省略しても同じ意味になります。angle が指定された場合、shapeを原点を中心として半時計回りに回転させます。

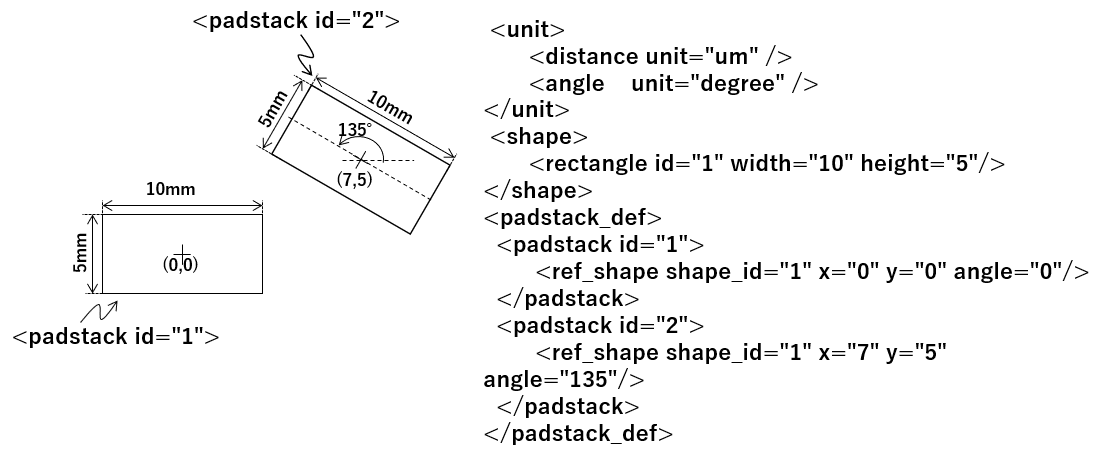

下に angle を使った少し複雑なpadstackの例を示します。このpadstackは2つのshapeによって構成されています。id="1"のshapeは原点(0,0)に配置され、id="2"のshapeは座標(7, 5)に135°回転して配置されています。

<module>要素

<module>要素には<socket>要素と<reference>要素を定義しています。

|

1 2 3 4 5 |

<module name="TPHR7904PB" type="PKG" shape_id="COMP_SHAPE_SOP_Advance_WF" x="0" y="0" angle="0" thickness="0.95" > <socket>要素 <reference>要素 </module> |

shape_id

idがCOMP_SHAPE_SOP_Advance_WFのshapeを参照しています。すなわTPHR7904PBの外郭形状は下図に示す図形となります。

angle

angleは0を定義しています。すなわち、このオプションは省略しても同じ意味となります。

thickness

部品の高さとして0.95mmを定義しています。

type

PKG (半導体パッケージ)を定義しています。

<socket>要素

TPHR7904PBの<socket>要素には、<port>と<portgroup>の2つの要素を定義しています。

|

1 2 3 4 |

<socket name="SOP_Advance_WF" > <port>要素 <portgroup>要素 </socket> |

これまでの例と異なり、TPHR7904PBの<socket>要素には<default>要素を定義して

いないことに注意してください。また、新たに<portgroup>要素も使用されています。

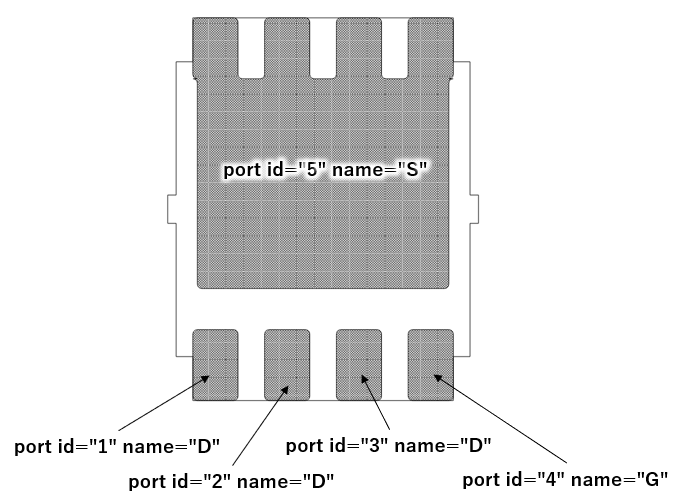

<port>要素

TPHR7904PBは電極(端子)を5つ持っています。<socket>要素には5つの<port>要素を定義しています。

また端子の形状の定義に<default>要素を使用していません。個々の<port>要素の shape_id 属性で端子の形状を定義しています。idが1から4の端子の形状はidがR80000X125000Fのpadstack、idが5の端子の形状はidがR_SOP_ADVANCE_WFのpadstackとなります。

|

1 2 3 4 5 |

<port id="1" padstack_id="R80000X125000F" x="-1905" y="-2750" angle="180" name="D" /> <port id="2" padstack_id="R80000X125000F" x="-635" y="-2750" angle="180" name="D" /> <port id="3" padstack_id="R80000X125000F" x="635" y="-2750" angle="0" name="D" /> <port id="4" padstack_id="R80000X125000F" x="1905" y="-2750" angle="0" name="G"/> <port id="5" padstack_id="R_SOP_ADVANCE_WF" x="0" y="0" angle="0" name="S" /> |

padstack_id

この端子の形状を定義しているpadstackの識別子を記載します。

<default>要素で端子形状が定義され、なおかつ<port>要素のpadstack_id属性でも端子形状が定義さえた場合は、padstack_id属性を優先します。

すなわち下記の2つの<socket>要素は同じ意味となります。

|

1 2 3 4 5 6 7 |

<socket name="SOP_Advance_WF" > <port id="1" padstack_id="R80000X125000F" x="-1905" y="-2750" angle="180" name="D" /> <port id="2" padstack_id="R80000X125000F" x="-635" y="-2750" angle="180" name="D" /> <port id="3" padstack_id="R80000X125000F" x="635" y="-2750" angle="0" name="D" /> <port id="4" padstack_id="R80000X125000F" x="1905" y="-2750" angle="0" name="G"/> <port id="5" padstack_id="R_SOP_ADVANCE_WF" x="0" y="0" angle="0" name="S" /> </socket> |

|

1 2 3 4 5 6 7 8 9 10 |

<socket name="SOP_Advance_WF" > <default> <port_shape padstack_id="R80000X125000F"/> </default> <port id="1" x="-1905" y="-2750" angle="180" name="D" /> <port id="2" x="-635" y="-2750" angle="180" name="D" /> <port id="3" x="635" y="-2750" angle="0" name="D" /> <port id="4" x="1905" y="-2750" angle="0" name="G"/> <port id="5" padstack_id="R_SOP_ADVANCE_WF" x="0" y="0" angle="0" name="S" /> </socket> |

angle

端子形状であるpadstackの回転角度を設定します。デフォルト値は0です。x y 属性で指定された座標にpadstackを配置し、反時計回りに回転させます。

name

端子の信号名を定義します。TPHR7904PBの例ではidが1と2と3の端子の信号名がD、idが4の信号名がG、idが5の端子がS/となっています。TPHR7904PBはMOS-FETなので、それぞれドレイン(D)、ゲート(G)、ソース(S)となります。識別子であるidは同一socket内でユニークである必要がりましたが、信号名であるnameはユニークの必要はありません

TPHR7904PBの端子形状は下図のようになります。

<portgroup>要素

<porggroup>要素は端子(port)をグルーピングして制約を与えます。様々な制約がありますが、このサンプルでは mustjoin 制約を与えています。

|

1 2 3 4 5 6 |

<portgroup name="drain> <mustjoin/> <ref_port id="1"/> <ref_port id="2"/> <ref_port id="3"/> </portgroup> |

name

ポートグループにユニークな名前を定義します。ここで定義したポートグループ名は、他の要素からポートグループを参照する際に使用されます。

<ref_port>要素

グルーピングする端子(port)を定義します。このサンプルではidが1と2と3の端子をグルーピングしています。

<mustjoin/>要素

<mustjoin>要素が定義されたグループは、グループに属する端子(port)はレイアウト設計時に必ず接続しなければならないことを意味します。このサンプルではidが1と2と3の端子、すなわち全てのドレイン端子はレイアウト設計時に必ず接続しなければなりません。

<reference>要素

<reference>要素で、この部品のシミュレーションモデルと端子との参照関係を定義します。サンプルはSPICEモデルの定義用とSパラモデルの定義用の2つの<reference>要素を含んでいます。

<reference>要素の構文規則

サンプルではSPICEモデルを参照する<reference>要素を定義しています。

TPHR7904PBは5つの端子を持ちますがFETであるため、実際の信号はソース(S)、ドレイン(D)、ゲート(G)の3つです。idが1から3の端子はドレイン(D)であるため、これらの端子はSPICEの同一のI/Oノードに接続されます。

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 |

<reference xmlns:spice="http://www.jeita.or.jp/LPB/spice" reffile = "TPHR7904PB.lib" format="SPICE" > <connection socket_name="SOP_Advance_WF" port_id="1"> <spice:ref_port subckt="NMOS_TPHR7904PB" portid="1"/> </connection> <connection socket_name="SOP_Advance_WF" port_id="2"> <spice:ref_port subckt="NMOS_TPHR7904PB" portid="1"/> </connection> <connection socket_name="SOP_Advance_WF" port_id="3"> <spice:ref_port subckt="NMOS_TPHR7904PB" portid="1"/> </connection> <connection socket_name="SOP_Advance_WF" port_id="4"> <spice:ref_port subckt="NMOS_TPHR7904PB" portid="2"/> </connection> <connection socket_name="SOP_Advance_WF" port_id="5"> <spice:ref_port subckt="NMOS_TPHR7904PB" portid="5"/> </connection> </reference> |

TPHR7904PBのC-FormatのportとSPICEモデルのI/Oノードの関係は下図のようになります。

今回はMOS FETを題材にポリゴン形状の記述方法に関して説明しました。C Formatはこのように任意形状の定義が可能となっています。次回からDDRを題材に設計制約の記述方法に関して説明を行います。

- DDR3