今回と次回はDDR3を題材としてより複雑なC-Formatについて学習します。前回までの内容に加え、新たに設計制約の定義方法に関しても説明します。

なお本連載では実際に存在する製品を例題にCFormatの解説を行ってきましたが、今回から例題とするDDR3は実存する部品ではありません。寸法や制約値は、説明の便宜上、仮想的に設定した値です。実際の設計制約ではありませんのでご了承ください。

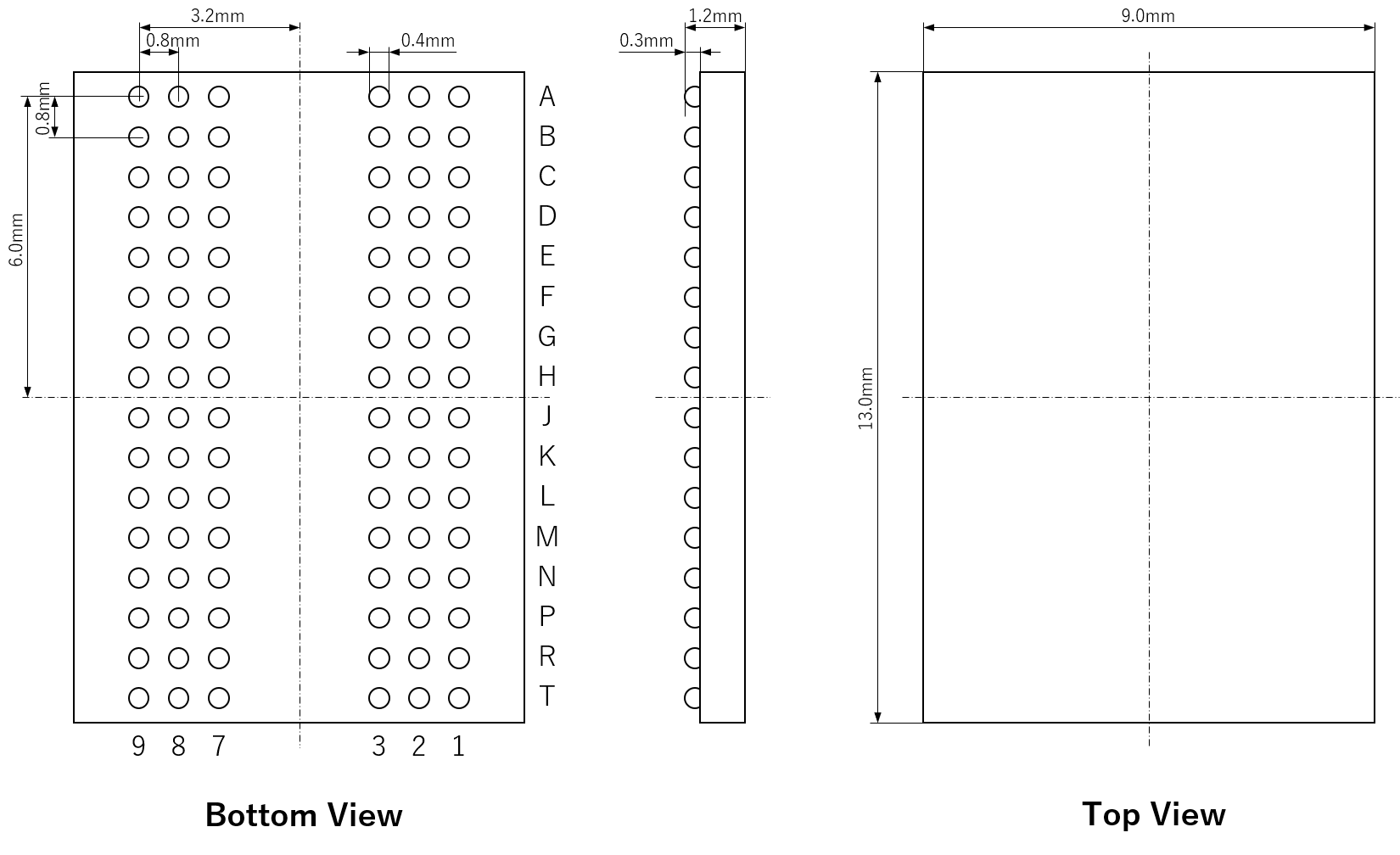

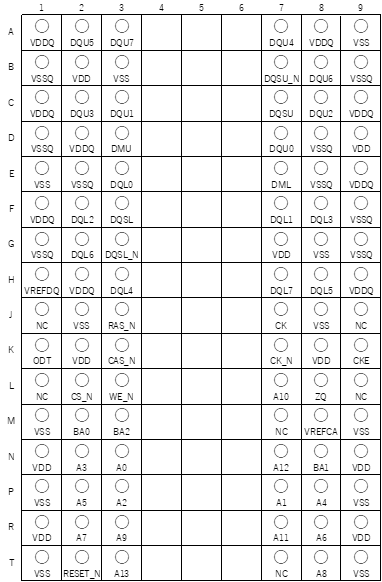

下に題材とするDDR3のパッケージレイアウト(DDR3 package layout)と端子マップ(DDR3 port map)を示します。以後このパッケージを例にC-Formatの説明を行います。

パッケージ形状の定義

まずC-Formatの基本であるパッケージの構造(外形形状と端子の形状)を定義します。既に前章までで形状の定義方法に関しては述べていますので、ここでは簡単に説明するにとどめます。

基本図形の定義

C-Format内で使用される形状は<global>要素内の<unit>, <shape>, <padstack_def>の子要素に定義します。以下にその例を示します。

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 |

<global> <unit> <distance unit="um"/> </unit> <shape> <rectangle id="boundary" width="9000" height="13000"/> <circle id="ball" diameter="400"/> </shape> <padstack_def> <padstack id="port"> <ref_shape shape_id="ball" x="0" y="0" pad_layer="BOTTOM"/> </padstack> </padstack_def> </global> |

<unit>要素

図形を定義する際に使用する長さの単位は<unit>要素内の<distance>子要素で定義します。この例では長さの単位としてミクロンメータを使用します。

|

1 2 3 |

<unit> <distance unit="um"/> </unit> |

<shape>要素

<shape>要素で基本図形を定義します。図面 DDR package layoutに示すように、このパッケージの外形は9000um×13000um(9mm×13mm)の長方形、端子は直径400um(0.4mm)の円形です。長方形は<rectangle>要素、円形は<circle>要素で定義します。

|

1 2 3 4 |

<shape> <rectangle id="boundary" width="9000" height="13000"/> <circle id="ball" diameter="400"/> </shape> |

id 属性は、ここの図形を参照するための識別子です。C-Formatファイル内でユニークである必要があります。

<padstack_def>要素

端子などの層構造を持つ図形(パッドスタック)は<padstack_def>要素で定義します。この例ではパッケージの下部に円形の端子を定義します。

|

1 2 3 4 5 |

<padstack_def> <padstack id="port"> <ref_shape shape_id="ball" x="0" y="0" pad_layer="BOTTOM"/> </padstack> </padstack_def> |

shape_id 属性に参照する図形の識別子 ball を定義します。端子はパッケージ下部に定義されるので pad_layer 属性はBOTTOM となります。。

パッケージ外形と端子の定義

下にパッケージ外形と端子を定義したC-Formatの例を示します。このパッケージには96個の端子がありますが、例では5個の端子だけを記載してます。完全な例はDDR-example を参照してください。

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 |

<module name="DDR3" shape_id="boundary" x="0" y="0" thickness="1200" type="PKG"> <socket name="ddrports"> <default> <port_shape padstack_id="port"/> </default> <port id="A1" x="-3200" y="6000" name="VDDQ" direction="inout" type="power"/> <port id="A2" x="-2400" y="6000" name="DQU5" direction="inout" type="signal"/> <port id="A3" x="-1600" y="6000" name="DQU7" direction="inout" type="signal"/> <port id="A7" x="1600" y="6000" name="DQU4" direction="inout" type="signal"/> <port id="A8" x="2400" y="6000" name="VDDQ" direction="inout" type="power"/> : </socket> </module> |

<module>要素

<module>要素の属性に部品の名称、外形および厚みを定義します。

|

1 |

<module name="DDR3" shape_id="boundary" x="0" y="0" thickness="900" type="PKG"> |

name 属性に部品名称、shape_id 属性にパッケージ外形の図形の識別子、

thickness にパッケージの厚みを定義します。このパッケージの例では厚みは900um(0.9mm)です。type にはモジュールのタイプを設定します。この例はICパッケージなので type 属性は PKG となります。

<socket>要素

パッケージの端子は<socket>要素の子要素で定義します。name 属性でソケットの名称を定義します。これはシミュレーションモデルと端子とのクロスリファレンスを定義するときに使用します。

<default>要素

<default>要素で端子の形状を定義します。子要素の<port_shape>要素で端子の形状を定義したpadstackを参照します。この例では端子の形状は port と名付けられたパッドスタックで定義されています。

|

1 2 3 |

<default> <port_shape padstack_id="port"/> </default> |

<port>要素

<port>要素でパッケージの端子を定義します。それぞれの端子の形状は<default>要素で定義されています。このパッケージには96個の端子がありますが、以下の例では5個の端子だけを記載してます。

|

1 2 3 4 5 |

<port id="A1" x="-3200" y="6000" name="VDDQ" direction="inout" type="power"/> <port id="A2" x="-2400" y="6000" name="DQU5" direction="inout" type="signal"/> <port id="A3" x="-1600" y="6000" name="DQU7" direction="inout" type="signal"/> <port id="A7" x="1600" y="6000" name="DQU4" direction="inout" type="signal"/> <port id="A8" x="2400" y="6000" name="VDDQ" direction="inout" type="power"/> |

id

端子の識別子(端子番号)です。同一socket内で識別子はユニークである必要があります。C-Formatの規定では id の付け方に定めはありませんが、広く一般的に使用されているルールに従うことを推奨します。この例ではJEDECルールに従って id を与えています。

x y

端子の配置座標です。端子形状のpadstackの原点を、ここで指定された座標に配置します。

name

端子名を設定します。端子名は id とは異なりユニークである必要はありません。この資料で使用している例では電源・グランド端子の端子名VDD 、 VDDQ 、 VSS 、 VSSQ はユニークではありません。

direction

信号の入出力方向を設定します。以下のいずれかを設定します。省略時は inout (双方向)となります。

inout - 入力

output - 出力

inout - 双方向

電源・グランド端子には信号の方向はありませんので、inout を設定します。

type

端子に入出力する信号のタイプを設定します。例示しているパッケージではsignal 、 power 、 ground の3種類だけが使われていますが、/以下の8種類のタイプがあります。いずれかの値を設定します。

power - 電源

ground - グランド

signal - 一般信号

floating - 如何なるネットにも接続してはならない端子です。この端子は未接続のままにしておくことを強制します。

dontcare - サーマルボールやnon-connectionのように論理的には意味を持たない端子

through - いわゆるフィードスルー端子と呼ばれる端子。フィードスルー端子は如何なる内部回路とも接続せず単にパッケージを貫通しているだけです

thermal - 熱端子です。VHDL-AMSやSPICEなどのシミュレーションモデルの熱端子と接続する場合に使用します。この端子に接続する熱(温度)の単位はK(Kelvin)です

thermal_c - thermalと同様な熱端子です。ただし、この端子に接続する熱(温度)の単位は ℃ (Celsius)です

制約の定義

既に<socket>要素の子要素の<default>と<port>は説明しました。<socket>要素は、これら以外に設計制約を定義するための子要素を持ちます。本章では、設計制約を定義するための子要素について説明します。以下は<socket>要素の構造です。

|

1 2 3 4 5 6 7 |

<socket name="ddrports"> <default>要素 <port>要素 <portgroup>要素 <constraint>要素 <swappable_port>要素 </socket> |

単位系の定義

形状の定義では使用する単位系は長さだけでした。ここでは、それに追加して制約で使用するインピーダンスと時間の単位を定義します。以下の例は時間単位としてピコセカンド、インピーダンス単位としてオームを定義した例です。

|

1 2 3 4 5 6 |

<unit> <impedance unit="ohm"/> <time unit="ps"/> <distance unit="um"/> <voltage unit="V"/> </unit> |

<time>

unit 属性で時間単位を設定します。以下のいずれかの値を設定します。もし時間単位の設定が省略された場合は、時間の単位は s (秒)となります。

ps - ピコ秒

ns - ナノ秒

us - マイクロ秒

ms - ミリ秒

s - 秒

<impedance>

unit 属性でインピーダンスの単位を設定します。以下のいずれかの値を設定します。もし設定が省略された場合は、インピーダンスの単位は ohm (Ω)となります。

fohm - フェムトΩ

pohm - ピコΩ

nohm - ナノΩ

uohm - マイクロΩ

mohm - ミリΩ

ohm - Ω

kohm - キロΩ

Mohm - メガΩ

<voltage>

unit 属性で電圧の単位を設定します。以下のいずれかの値を設定します。もし設定が省略された場合は、電圧の単位は V となります。

pV - ピコボルト

nV - ナノボルト

uV - マイクロボルト

mV - ミリボルト

V - ボルト

kV - キロボルト

<portgroup>要素

<portgroup>要素(端子グループ)は、ある特定の意味を持つ端子の集まりで、これに対し様々な制約を与えることができます。

先ず、基本的な端子グループの作り方を見ていきましょう。下記記述は、DDR3のLowチャネルのデータストローブの差動信号の端子(DQSL, DQSL_N)をグルーピングして DATASTROB_L というグループ名を与えています。

|

1 2 3 4 |

<portgroup name="DATASTROB_L"> <ref_port name="DQSL"/> <ref_port name="DQSL_N"/> </portgroup> |

また以下はLowチャネル側のデータ端子(DQL0~ DQL7)をグルーピングして DATA_L というグループ名を与えた例です。

|

1 2 3 4 5 6 7 8 9 10 |

<portgroup name="DATA_L"> <ref_port name="DQL0"/> <ref_port name="DQL1"/> <ref_port name="DQL2"/> <ref_port name="DQL3"/> <ref_port name="DQL4"/> <ref_port name="DQL5"/> <ref_port name="DQL6"/> <ref_port name="DQL7"/> </portgroup> |

<portgroup>要素の name 属性

グループ名です。グループ名は<socket>要素内でユニークである必要が有ります。

<ref_port>要素

<ref_port>要素でグルーピングする端子を定義します。例では端子名(name)で端子を参照していますが、端子番号(id)で参照することもできます。以下は端子番号でDQSL, DQSL_Nをグルーピングした例です。

|

1 2 3 4 |

<portgroup name="DATASTROB_L"> <ref_port id="F3"/> <ref_port id="G3"/> </portgroup> |

ここで、端子名でのグルーピングと端子番号でのグルーピングの記述方法の違いを説明するために別の例を示します。このDDRの例はVSSとVSSQの2つのグランドを持ちます。このグランド端子をグルーピングする例を考えます。端子名で記載する場合は以下のようになります。すなわち端子名がVSSもしくばVSSQである21個の端子がグループとなります。

|

1 2 3 4 |

<portgroup name="GND"> <ref_port name="VSS"/> <ref_port name="VSSQ"/> </portgroup> |

これに対し端子番号で参照する場合は、一つ一つの端子を個別に設定します。

以下のような記述になります。

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 |

<portgroup name="GND"> <ref_port id="A9"> <ref_port id="B1"> <ref_port id="B3"> <ref_port id="B9"> <ref_port id="D1"> <ref_port id="D8"> <ref_port id="E1"> <ref_port id="E2"> <ref_port id="E8"> <ref_port id="F9"> <ref_port id="G1"> <ref_port id="G8"> <ref_port id="G9"> <ref_port id="J2"> <ref_port id="J8"> <ref_port id="M1"> <ref_port id="M9"> <ref_port id="P1"> <ref_port id="P9"> <ref_port id="T1"> <ref_port id="T9"> </portgroup> |

以上2つの記載方法は、いずれも同じ意味となります。状況によって使い分けてください。

差動信号

ストローブ信号の例に戻ります。グループした端子が差動信号であることを明示したいときは、以下のように端子グループに <differential/> を追加します。また正信号/負信号を表す polarity 属性を追加します。

|

1 2 3 4 5 |

<portgroup name="DATASTROB_L"> <differential/> <ref_port name="DQSL" polarity="POSITIVE"/> <ref_port name="DQSL_N" polarity="NEGATIVE"/> </portgroup> |

polarity

作動信号の正信号および負信号を表す属性です。以下のいずれかを設定します。

POSITIVE - 正信号

NEGATIVE - 負信号

では、この信号にインピーダンスとスキューの制約を追加してみます。これらの制約は<constraint>要素の子要素として定義します。

今回はDDR3パッケージの形状と、端子グループおよび作動信号の定義について説明ました。次回は電源の定義やスキュー制約の定義方法を紹介します。