前回に引き続きDDR3を題材にCFormatでの設計制約の記述方法に関して説明します。今回は、インピーダンスやスキューの制約、電源の定義を行います。

インピーダンス制約

インピーダンス制約は<impedance>要素で定義します。下はデータ信号(DQL0~DQL7)に対し50 Ω ± 10%のインピーダンス制約を与える例です。

|

1 2 3 4 5 6 7 8 9 10 |

<constraint> <impedance port_name="DQL0" min="45" typ="50" max="55"/> <impedance port_name="DQL1" min="45" typ="50" max="55"/> <impedance port_name="DQL2" min="45" typ="50" max="55"/> <impedance port_name="DQL3" min="45" typ="50" max="55"/> <impedance port_name="DQL4" min="45" typ="50" max="55"/> <impedance port_name="DQL5" min="45" typ="50" max="55"/> <impedance port_name="DQL6" min="45" typ="50" max="55"/> <impedance port_name="DQL7" min="45" typ="50" max="55"/> </constraint> |

port_name

インピーダンス制約を与える端子名です。

typ/min/max

インピーダンス値を設定します。 公差を設定しない場合は min 、 max は不要です。下の例は公差を定義しない例です。

|

1 2 3 4 5 6 7 8 9 10 |

<constraint> <impedance port_name="DQL0" typ="50"/> <impedance port_name="DQL1" typ="50"/> <impedance port_name="DQL2" typ="50"/> <impedance port_name="DQL3" typ="50"/> <impedance port_name="DQL4" typ="50"/> <impedance port_name="DQL5" typ="50"/> <impedance port_name="DQL6" typ="50"/> <impedance port_name="DQL7" typ="50"/> <constraint> |

上記の例では端子毎に制約を与えていますが、端子グループを使って一括で制約を与えることもできます。下の例はデータ信号(DQL0~DQL7)をグループ化し、グループ全体に50 Ω ± 10%のインピーダンス制約を与えています。

|

1 2 3 4 5 6 7 8 9 10 11 12 13 |

<portgroup name="DATA_L"> <ref_port name="DQL0"/> <ref_port name="DQL1"/> <ref_port name="DQL2"/> <ref_port name="DQL3"/> <ref_port name="DQL4"/> <ref_port name="DQL5"/> <ref_port name="DQL6"/> <ref_port name="DQL7"/> </portgroup> <constraint> <impedance group_name="DATA_L" min="45" typ="50" max="55"/> </constraint> |

group_name

インピーダンス制約を与える端子グループの名称です。

差動信号に作動インピーダンスを定義する場合は、作動信号を定義した端子グループに対して制約を与えます。下の例は、データストローブ信号に100 Ω ± 10%の差動インピーダンス制約を設定した例です。

|

1 2 3 4 5 6 7 8 |

<portgroup name="DATASTROB_L"> <differential/> <ref_port name="DQSL" polarity="POSITIVE"/> <ref_port name="DQSL_N" polarity="NEGATIVE"/> </portgroup> <constraint> <impedance group_name="DATASTROB_L" type="differential" min="90" typ="100" max="110"/> </constraint> |

type

以下の3つの何れかを設定します。省略可能です。省略時はシングルエンド・インピーダンスを意味します。

single - シングルエンド・インピーダンス。デフォルト値

differential - 差動インピーダンス

common - コモンモード・インピーダンス

スキュー制約

スキューの制約は<skew>要素で定義します。例えばデータストローブ信号の差動信号間の遅延差(skew)を5psに設定する場合は、以下のように記述します。

|

1 2 3 |

<constraint> <skew group_name="DATASTROB_L" max="5"/> </constraint> |

また、データ信号の信号間の遅延(skew)を5psに設定する場合は、以下のように記述します。

|

1 2 3 |

<constraint> <skew group_name="DATA_L" max="5"/> </constraint> |

group_name

スキュー制約を与える信号のグループ名を設定します。ここで参照しているグループに属する信号の遅延差を max 属性で与えた値以下に抑えることを要求します。

max

許容される最大スキュー値を設定します。

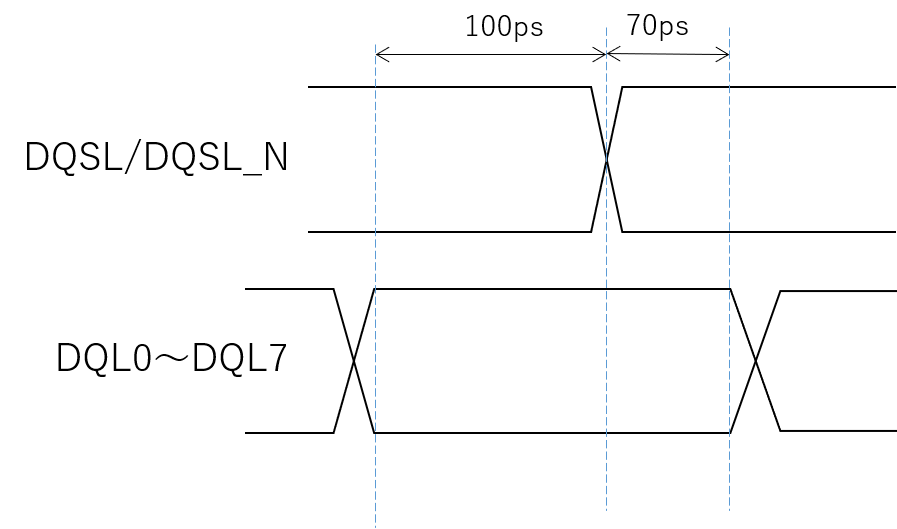

スキュー制約には、スキューの基準信号(reference_port_name)を設定することができます。この記述方法は、例えば 下図(DQS_VS_DQ_Timing_Chart) のタイミングチャートようなデータストローブとデータ信号の関係の制約を設定する際に使用します。

|

1 2 3 4 5 6 7 8 9 10 11 12 13 |

<portgroup name="DATA_L"> <ref_port name="DQL0"/> <ref_port name="DQL1"/> <ref_port name="DQL2"/> <ref_port name="DQL3"/> <ref_port name="DQL4"/> <ref_port name="DQL5"/> <ref_port name="DQL6"/> <ref_port name="DQL7"/> </portgroup> <constraint> <skew group_name="DATA_L" reference_port_name="DQSL" max="70" min="-100"/> </constraint> |

reference_port_name

スキューの基準信号となる端子名

電源設定

本稿で使用しているDDRの例にはVDDQ/VSSQ(DQ用の電源・グランド)とVDD/VSS(DQ以外の電源・グランド)の2つの電源系統があります。C-Formatには、これらの電源系統は<powerdomain_group>要素で定義します。

電源定義はデジタル・アナログが混載したICで、それぞれの専用電源とそれに対応する信号を定義する場合などに使用します

まず、それそれの電源系統の電圧を定義しましょう。1.5V±5%とすると以下のような記述になります。

|

1 2 3 4 5 6 |

<powerdomain_group pwr_port_name="VDDQ" pwr_min="1.425" pwr_typ="1.5" pwr_max="1.575" gnd_port_name="VSSQ" gnd_typ="0"/> <powerdomain_group pwr_port_name="VDD" pwr_min="1.425" pwr_typ="1.5" pwr_max="1.575" gnd_port_name="VSS" gnd_typ="0"/> |

pwr_port_name/gnd_port_name

pwr_port_name に電源端子名を、 gnd_port_name に、それと対となるグランド端子名を定義します。

pwr_min/pwr_typ/pwr_max/gnd_min/gnd_typ/gnd_max

pwr_typ で電源電圧を定義します。公差を定義する場合は、 pwr_min 、 pwr_max に最小許容電圧値、最大許容電圧値を定義します。このサンプルの例では電源電圧 1.5V、± 5%の公差なので pwr_min="1.425" pwr_typ="1.5" pwr_max="1.575" と定義しています。

同様に gnd_typ でグランド電圧、 gnd_min 、 gnd_max最小許容電圧値、最大許容電圧値を定義します。

以上の例ではグランドをVSSQとVSSの2種類に分割していますが、単一グランドとして定義する場合は、端子グループを使用して以下のように記述します。

|

1 2 3 4 5 6 7 8 9 10 |

<portgroup name="GND"> <ref_port name="VSS"/> <ref_port name="VSSQ"/> </portgroup> <powerdomain_group pwr_port_name="VDDQ" pwr_min="1.425" pwr_typ="1.5" pwr_max="1.575" gnd_group_name="GND" gnd_typ="0"/> <powerdomain_group pwr_port_name="VDD" pwr_min="1.425" pwr_typ="1.5" pwr_max="1.575" gnd_group_name="GND" gnd_typ="0"/> |

pwr_group_name/gnd_group_name

pwr_group_name で電源端子の端子グループ、 gnd_group_nameでグランド端子の端子グループを定義します。

以上に加え各電源系統に、それに対応する信号を割り当てることができます。例えばDDRではVDDQはデータ信号(DQ)の専用電源となりますが、これを明示的に定義する場合は、<powerdomain>要素の子要素に電源系統に割り当てる信号(端子)を定義します。下記はVDDQ/VSSQの電源系統とDQL/DQUのデータ信号の関係を明記した例です。

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 |

<portgroup name="DATA_L"> <ref_port name="DQL0"/> <ref_port name="DQL1"/> <ref_port name="DQL2"/> <ref_port name="DQL3"/> <ref_port name="DQL4"/> <ref_port name="DQL5"/> <ref_port name="DQL6"/> <ref_port name="DQL7"/> </portgroup> <portgroup name="DATA_U"> <ref_port name="DQU0"/> <ref_port name="DQU1"/> <ref_port name="DQU2"/> <ref_port name="DQU3"/> <ref_port name="DQU4"/> <ref_port name="DQU5"/> <ref_port name="DQU6"/> <ref_port name="DQU7"/> </portgroup> <powerdomain_group pwr_port_name="VDDQ" pwr_min="1.425" pwr_typ="1.5" pwr_max="1.575" gnd_port_name="VSSQ" gnd_typ="0"> <ref_portgroup name="DATA_L"/> <ref_portgroup name="DATA_U"/> </powerdomain_group> |

端子の交換

DDRでは同じバイトレーン内のデータ信号は交換可能です。すなわちDQL0~DQL7は互いに交換可能です。同様にDQU0~DQU7も交換可能です。C-Formatで、これを明示的に定義するには<socket>要素の下の、<swappable_port> を使用します。 以下に、その例を示します。<ref_port>要素の name 属性 に端子名を設定します。<swappable_port>内で参照された端子は、互いに交換可能であることを意味します。

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 |

<swappable_port> <ref_port name="DQL0"/> <ref_port name="DQL1"/> <ref_port name="DQL2"/> <ref_port name="DQL3"/> <ref_port name="DQL4"/> <ref_port name="DQL5"/> <ref_port name="DQL6"/> <ref_port name="DQL7"/> </swappable_port> <swappable_port> <ref_port name="DQU0"/> <ref_port name="DQU1"/> <ref_port name="DQU2"/> <ref_port name="DQU3"/> <ref_port name="DQU4"/> <ref_port name="DQU5"/> <ref_port name="DQU6"/> <ref_port name="DQU7"/> </swappable_port> |

上の例では端子名で交換可能な端子を参照していましたが、端子番号( id ) で参照することも可能です。以下に、その例を示します。<ref_port>要素の id 属性に端子番号を設定します。

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 |

<swappable_port> <ref_port id="A2"/> <ref_port id="A3"/> <ref_port id="A7"/> <ref_port id="B8"/> <ref_port id="C2"/> <ref_port id="C3"/> <ref_port id="C8"/> <ref_port id="D7"/> </swappable_port> <swappable_port> <ref_port id="E3"/> <ref_port id="F2"/> <ref_port id="F7"/> <ref_port id="F8"/> <ref_port id="G2"/> <ref_port id="H3"/> <ref_port id="H7"/> <ref_port id="H8"/> </swappable_port> |

以上、DDR3を題材にCFormatでの設計制約の定義方法について説明しました。次回はIEEE2401-2019でCFormatに追加された新機能を紹介します。

- CFormatの新機能(IEEE2401-2019)