開催日時:2017年6月30日(金)10:00~17:00

場所:新横浜国際ホテル マナーハウス

〒 222-0033 横浜市港北区新横浜 3-18-1

公式ホームページ:http://dvcon-japan.com/2017/

参加申し込み:http://dvcon-japan.com/2017/?page_id=23

DVConとは

価値のある魅力的な製品を生み出すためには新たなモノのコンセプトを作り上げ、そのコンセプトを製品化するための革新的な設計技術と検証方法が必要です。この設計&検証の議論する場がDVCon(Design and Verification Conference)の基本思想です。現在、US、Europe、India、Chinaで開催されており、2017年より日本でも始まります。

DVCon Japanの特徴

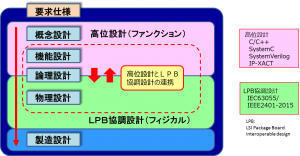

DVCon JapanにおいてはDVConの基本思想をベースにして、日本の得意とする物作りのための技術を活かした独自アイディアを加えることを考えており、上流設計におけるファンクションとLPB協調設計におけるフィジカルを連携させ、システムとしての完成度を上げていくことをテーマとして議論していくことを考えています。

予定トラック

- SystemCトラック : SystemCを用いた上流設計手法

- Verificationトラック : 標準言語を用いたハードウェア検証手法

- LPBトラック : システム開発におけるLPB相互設計&高位設計連携

LPBトラック

独自のア イディアとして日本の得意とする物作りのための技術を活かしたLPB相互設計と高位設計を連携させ、システムとしての完成度を上げていくことをテーマとして議論していくことを考えています。

イディアとして日本の得意とする物作りのための技術を活かしたLPB相互設計と高位設計を連携させ、システムとしての完成度を上げていくことをテーマとして議論していくことを考えています。

プログラム

10:40-11:50 基調講演:IoT、車載におけるフロントローディング型設計

IoT時代の設計手法

大阪大学 今井名誉教授

車載製品の企画・構想段階における仮想開発手法

(株)デンソー 基盤ハードウェア開発部 ハード開発改革室 課長

荒井総一郎 (あらい そういちろう)

車載電子システムの高機能化、低コスト化両立のため、車載電子製品は機電一体に代表される複雑な形態が求められている。これらの製品の設計難易度は非常に高く、仮想開発による早期成立性検証が必須となるが、情報量の不足する企画・構想段階ではシミュレーション活用が困難である。本講演ではシステム,エレ,メカの開発プロセスを段階的に紐付け、不足する情報を相互に補いながら製品を具体化する仮想開発手法を説明する。

12:50-13:20 ワークショップ:システム品質を上流で押さえるための課題

〜 困りごと・悩みを聞いてください 〜

(株)東芝 半導体研究開発センター設計技術開発部 参事

冨島 敦史 (とみしま あつし)

上流・下流という言葉は人によって定義は異なりますが、通じないな」という関係はありませんか?決して仲が悪いわけではないが、なんだか上手くいかない。昔は設計の全ての工程を、一個人(一部所)が担当していましたが、今は役割が分担され、それぞれの担当範囲が不文律として成立してしまいました。 上流、下流を区別する必然性 とは何でしょうか?上流から下流、あるいは下流から上流へのお互い関心を持たなくなっていませんか?設計工程で最も大切な情報流通がなくなり、情報伝達手段の取り決めも無い まま、分業化というものだけが先行したのではないでしょうか? どこかに歪を抱えながら設計を進めていると思うことはありませんか?

ワークショップでは、敢えて上手く行ってない関係を取り上げて話し合います。 これは LPBトラックの主テーマでもあります。スポンサー事例やパネル ディスカッションでは、この投げかけに対してどの様に答えてくれるでしょうか? 皆様のご参加をお待ちしています。

13:20-14:00 『設計上流でシステム(LPB)シミュレーションは可能か?その鍵とは?』

アンシス・ジャパン株式会社

技術サポートチーム エレクトロニクス製品グループ マネージャ

渡辺 亨(わたなべ とおる)

昨今の電子機器設計者からの要望として、より設計の上流でEMCシミュレーションを行いた

いという声を時折耳にする。本セッションでは、初めに自動車のADASの(1D)シミュレーション事例を紹介する。ここで鍵となるROM(次数低減モデル)とは何か?LSI-パッケージ-ボードのシミュレーションにおけるROMとは?また、SI・PI、そしてEMCシミュレーションの設計上流への展開の可能性について考察する。

14:00-14:30 『構想設計における連携どうする』

(株) ジェム・デザイン・テクノロジーズ 代表取締役

村田 洋 (むらた ひろし)

一歩進んだ製品を一歩早く生み出すには、できるだけ上流の段階から、関係者の縦連携を

進めることがカギになります。LPBフォーマットの登場により、その気があれば、ノートの切れ端にポンチ絵を書くような段階から、製品情報をネットに載せて流すことができるようになりました。本講演では、その具体例を弊社トレーニングの現場データから紹介するとともに、

ではそれが実際の連携にどうつながるか、という点について述べます。

15:00-15:30 『システム全体構想をどう物理設計に展開していくか?』

(株)図研 EDA事業部EL開発部 シニア・マネージャー

松澤 浩彦(まつざわ ひろひこ)

電子機器のシステム全体の構想設計において、軽量化・高性能化と、低コスト化などを両立させることは重要である。旧モデルや過去の設計資産を、プリント基板や筐体外観を参照しながら、論理面/物理面から検討し、設計仕様を創っていく流れを紹介する。またその結果の設計仕様を詳細の物理設計(熱やEMCを考慮した設計)に展開していく事例紹介、現状の仮題、今後の展開についても触れる。

15:30 – 16:10 : ポスター展示

スポンサー企業様、登壇者様との交流の場です。発表に関する議論はこちらでどうぞ。

16:20-17:30 パネルディスカッション:システム品質向上のための連携

〜 悩みに対する答えを探そう! 〜

モデレータ: (株)東芝 半導体研究開発センター設計技術開発部 主幹

福場 義憲 (ふくば よしのり)

DVCon Japan LPBトラックでは現在最も注目されているIoTと車載アプリケーションを対象 に、いかに製品品質を確保するかを議論して行きます。一言にIoTや車載と言っても、最終製品の使用場面により多様な設計ターゲットが求められています。短期間で開発を完了させるためには、設計ターゲットを開発行程の早期に決定する必要があります。しかし、現実には設計の初期段階では最終製品の使用場面を十分に考慮 できず、多くの特性面での課題が後工程、すなわち物理設計段階で発覚し設計の手戻りが 多発しています。

パネルディスカッションでは当日の公演で発表された提案や事例のキーワードを集め、この 課題の解決方法を討議します。具体的には、設計行程の上流部分で準備すべきモデルと 下流部分での事例や資産などから得られるモデルを収集し、新たな検証段階を実現する 方法を探ります

パネラー:

大阪大学 大学院情報科学研究科 名誉教授

今井 正治 (いまい まさはる)様

(株)デンソー 基盤ハードウェア開発部 ハード開発改革室 課長

荒井 総一郎 (あらい そういちろう)様

MAGILLEM JAPAN

Field Application Engineer

中村 幸二 (なかむら こうじ)様

アンシス・ジャパン株式会社

技術サポートチーム エレクトロニクス製品グループ マネージャ

渡辺 亨(わたなべ とおる) 様

(株) ジェム・デザイン・テクノロジーズ 代表取締役

村田 洋 (むらた ひろし)様

(株)図研 EDA事業部EL開発部 シニア・マネージャー

松澤 浩彦(まつざわ ひろひこ)様

(株)東芝 半導体研究開発センター設計技術開発部 参事

冨島 敦史 (とみしま あつし)様

スポンサー企業

アンシス・ジャパン株式会社

ANSYSは、1970年から40年以上にわたり、構造から流体、電磁場、システム・回路まで、幅広い領域にまたがる総合的CAEソリューションを世界中のお客様に提供しています。今回は半導体を主として、プリント配線板、筐体、車体までを対象に、IC電源品質および信頼性、シグナル・パワーインテグリティ、エミッションとイミュニティといった問題への包括的なソリューションを紹介致します。

【展示製品】

半導体設計向け:

- ANSYS RedHawk -SoCパワー、ノイズ、信頼性検証プラットフォーム。プロトタイピングからサインオフまで最新テクノロジーノード(~7nm)に対応。

- ANSYS Power Artist-RTLパワープラットフォーム。RTL消費電力解析、パワーリダクション、パワープロファイリングなど包括的なソリューションを提供。

プリント基板、筐体、車体設計向け:

- ANSYS HFSS/Q3D Extractor/SIwave-3D/2D電磁界解析および回路シミュレータ。

- ANSYS Icepak-電気・電子機器熱流体解析ツール。

- ANSYS Simplorer-マルチドメイン回路・システムシミュレータ。

ウエブサイト: http://www.ansys.com/ja-JP

http://www.ansys.com

(株)ジェム・デザイン・テクノロジーズ

弊社は2008年創立の国産EDAツール開発会社です。主力製品のGemPackageはチップ・パッケージ・ボード コデザイン構想設計ツールです。2012年よりLPBフォーマットのワークグループに参画し、継続的に規格制定の議論や国際化の過程をつぶさに拝見することができ、そのおかげで、当初ICパッケージ用のフィージビリティスタディツールであったGemPackageを、チップ・パッケージ・ボードのコデザインツールへと進化させることができました。

展示では、弊社のお客様の事例発表資料を配布いたします。資料の電子配布はできませんので、ぜひこの機会に、お立ち寄りお手にとってご覧ください。

ウエブサイト: http://www.gemdt.com/

http://www.gemdt.com/en/

株式会社 図研

図研は、1976年創業以来40年に渡り、世界のモノづくりをITソリューションで支えてきました。

図研のエレクトロニクス設計ソリューションは、構想設計から詳細実装設計、製造設計まで幅広い領域をカバーしています。 LSI、パッケージ、PCBなど複数の異なるオブジェクトをシステムとして設計・検証するパワーをもつ最新のCR-8000シリーズをはじめとして、最先端のエレクトロニクス設計環境を提供しています。 またこれらのツールの導入にあたっては、国内外の数多くの先進企業での導入実績にもとづく知見と経験豊かなスタッフによるきめ細かなコンサルティングや専門分野でのサポートも実施しています。今回の展示では、構想設計段階での使用するEDA技術と、詳細設計段階でのEMC/熱といった実装に係るEDA技術をご紹介します。

ウエブサイト: http://www.zuken.co.jp/

http://www.zuken.co.jp/en/

株式会社ジーダット

ジーダットは、Custom LSI、Power MOS Design、Flat Panel Designで新たな設計ソリューションをご提供します。

【展示製品】

Custom LSI

SX-Meisterによるカスタムデザイン用フロアプラ

- 業界初の抵抗制約ドリブン電源配線用自動ルータ

配線領域と配線形状を自動的に割り当て、EM/IR drop/ノイズなどを制約条件として考慮し、マージンの少ない最適な電源配線を実現します。 - トップ階層設計において、ネットドリブン環境を保持しながら、レイアウトに最適な階層を構築するとで、設計効率を向上します。

Power MOS Design

PowerVoltにより、フルチップのPower MOSに対し電気特性を高速に解析し、設計最適化やサインオフを効率化します。

- スタティック解析:電流/電圧/パワー分布/On抵抗

- ダイナミック解析:ポート電流/電圧波形、時刻ごとの電流/電圧分布

- 熱解析:定常熱分布、ボンディングやパッドの境界条件設定

Flat Panel Design

SX-Meisterによるフラットパネルディスプレイの設計環境

- IoT、スマホ、車載などで要求される任意形状の配線の高速一括配線を行います。

- LSIに比較して長大な任意形状配線の抵抗・容量を液晶専用のツールで高速・高精度に抽出します。

ウエブサイト: http://www.jedat.co.jp/

http://www.jedat.co.jp/eng/index.html

参加登録はこちらから