DVConが近付いて参りました。今回は「DVConステアリングTG」からお届けします。

DVCon Japan 2024開催決定!

来る2024年8月29日、第3回目のDVCon Japanが開催されます!

会場はTKPガーデンシティPREMIUM品川高輪口で、品川駅から歩いて1〜2分のところにあります。午前中は基調講演やAccelleraのアップデートを中心に、午後は論文発表やチュートリアルを中心にプログラムが進む予定です。また併設してスポンサーや出展者によるソリューション展示も開催しますし、夕方にはネットワーキングイベントとして懇親会も行う予定でいます。

DVCon JapanのWebサイトも継続的に更新されています。是非ともDVCon JapanのWebサイトをお気に入りやブックマークに登録していただき、今後のアップデートにご注目ください。

DVConとは

ここで改めてDVConとは何かについて触れておきましょう。

DVConは正式にはDesign & Verification Conference & Exhibitionであり、電子システムおよび集積回路の設計と検証のための言語、ツール、メソドロジ、標準の適用に関する最高峰のカンファレンスです。このカンファレンスはAccellera Systems Initiativeがメインスポンサーとなり、非常に技術的なコンテンツで構成されており、設計と検証の技術の実用的な側面や、最先端プロジェクトにおける活用に焦点を当てています。参加者が同様の技術を参考にしたり採用したりすることで、自身の設計や検証のフローの改善が促進され、ひいては業界全体の技術水準が高まることを目指しています。

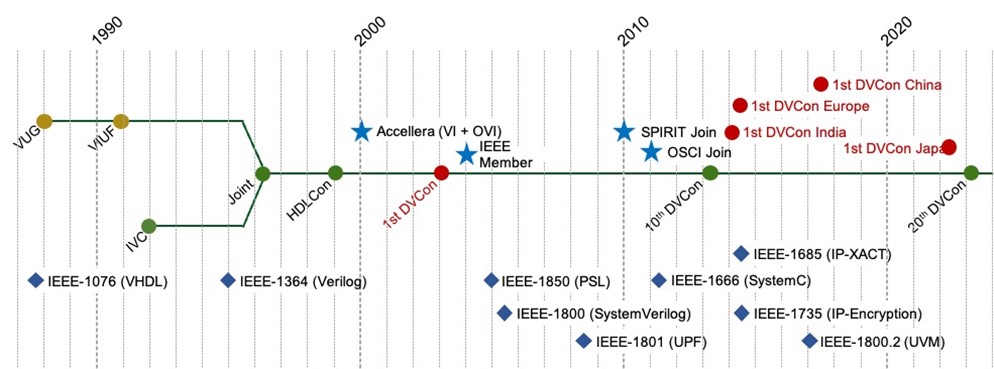

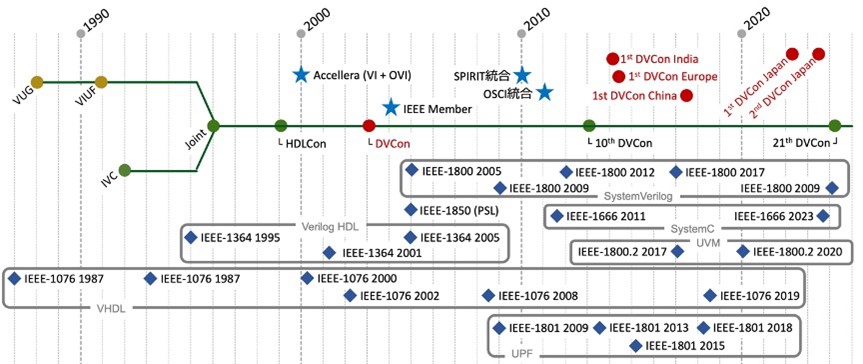

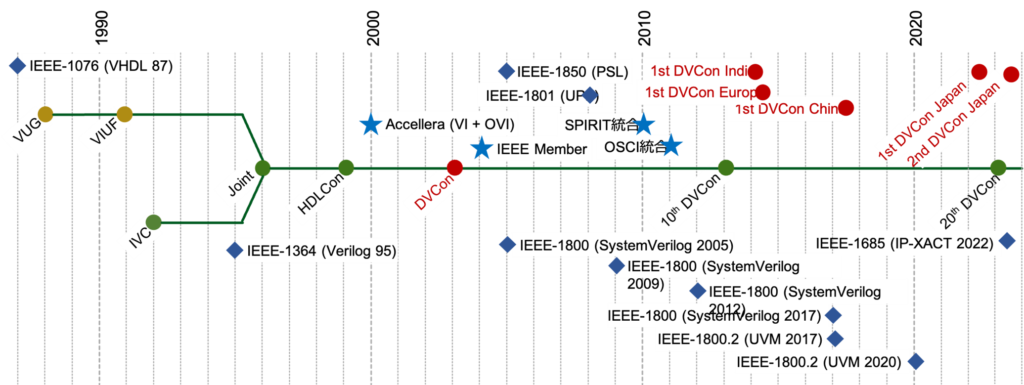

DVConの歴史を紐解くと、VHDL User's GroupとInternational Verilog Conferenceにまで遡ります。当時言語戦争とまで言われたVHDLとVerilogの両陣営のコミュニティは、両言語混在の商用シミュレータの登場により、両言語の資産やノウハウが最も共有される形で、HDLConとして融合しました。一方でムーアの法則に従うように半導体の集積度が上がるにつれ、設計生産性の課題と検証生産性の課題が議論されるようになりました。こと検証生産性の課題は顕著であり、アサーションや制約付きランダム検証、機能カバレッジなどの検証技術が出現し、独自言語が乱立する中で標準化の必要性がかつてないほど重要になってきました。このような背景から、業界における標準化を加速する目的でAccelleraが生まれました。そしてHDLConはDVCon = Design and Verification Conferenceと改められ、今日に至っています。AccelleraはDVConにおけるさまざまな議論を元に、標準化のWorking Groupを設立し、実に多くの標準を策定してはIEEEに寄贈する形で業界への貢献を継続しています。

DVConは米国で始まり、その後ヨーロッパやインド、そして中国でも開催されるようになります。長く待たれていた日本国内でのDVConは2022年に第1回目がオンライン+オンデマンド形式で開催されました。そして2023年には初めて対面での開催となり、様々な論文発表や懇親会、ベストペーパーアワードなど、大変盛り上がりを見せるカンファレンスとなりました。

Call for Paper / Call for Tutorial

DVCon Japan 2024は8月29日の開催です。すでにCall For Paper、Call For Tutorialがオープンしていますので、奮ってご投稿ください。完全な論文でなくても、数ページのプレゼンテーションスライドで応募していただくことも可能です。ご不明な点があれば、メールでお問い合わせください。

→ info@dvcon-jpn.org

最後に

DVCon Japanの実行委員会では、実行委員を募集しています。現在は10名程度ですが、より中身の濃い、より学ぶことの多いカンファレンスとしていくために、いっしょに企画・運営していただける方、仕事も忙しいけどちょっと外部の人たちと交流することで活躍するフィールドを広げたいと思っている方、大歓迎です。

(EE Tech Focus合同会社 / 三橋明城男)

鶴岡慶雅先生

鶴岡慶雅先生