жЬАињСгБЃгБКзЯ•гВЙгБЫ

- 2025-3-26

-

зђђ126еПЈ LPBгГЛгГ•гГЉгВєпЉИLPBгВЈгВєгГЖгГ†гВљгГ™гГ•гГЉгВЈгГІгГ≥гГХгВ©гГЉгГ©гГ† и≥ЗжЦЩжО≤иЉЙ)

- 2025-3-5

-

зђђ125еПЈ LPBгГЛгГ•гГЉгВєпЉИLPBгВЈгВєгГЖгГ†гВљгГ™гГ•гГЉгВЈгГІгГ≥гГХгВ©гГЉгГ©гГ†жШОжЧ•зФ≥гБЧиЊЉгБњзЈ†еИЗ)

- 2025-3-3

-

зђђ124еПЈ LPBгГЛгГ•гГЉгВєпЉИLPBгВЈгВєгГЖгГ†гВљгГ™гГ•гГЉгВЈгГІгГ≥гГХгВ©гГЉгГ©гГ†дїКйА±жЬЂйЦЛеВђ!)

About Us

JEITA еНКе∞ОдљУпЉЖгВЈгВєгГЖгГ†йЦЛзЩЇжКАи°УгВµгГЦгВ≥гГЯгГГгГЖгВ£гБѓгАБгАМеНКе∞ОдљУгАНгБ®гАМгВЈгВєгГЖгГ†гАНгБЃи®≠и®ИжКАи°УгБЃиЮНеРИпЉИеНФи™њи®≠и®ИпЉЙгВТзЫЃжМЗгБЧгБ¶жіїеЛХгБЧгБ¶гБДгБЊгБЩгАВ

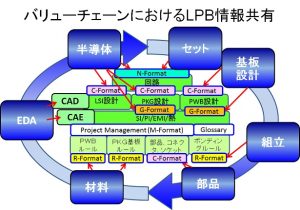

йЫїе≠Рж©ЯеЩ®гБЃйЦЛзЩЇгГїи≤©е£≤гБЃж∞іеє≥еИЖж•≠гБМйА≤гВАдЄ≠гАБзЂґдЇЙеКЫгБМгБВгВЛи£љеУБгВТеЄВе†іжКХеЕ•гБЩгВЛгБЂгБѓгВµгГЧгГ©гВ§гГБгВІгГЉгГ≥гБЃдЄ≠гБЂжХ£еЬ®гБЩгВЛжКАи°УгВТгВњгВ§гГ†гГ™гГЉгБЂиЮНеРИгБЧгАБеХЖеУБдЉБзФїгВТзЈігВЛгБУгБ®гБМдЄНеПѓжђ†гБІгБЩгАВгБЭгБЃзВЇгБЂгБѓеАЛгАЕгБЃжКАи°УгБЃжµБйАЪжАІгБМйЗНи¶БгБ®гБ™гВКгБЊгБЩгАВжИСгАЕгБМдЉБзФїгБЧгБЯLSIгГїгГСгГГгВ±гГЉгВЄгГїгГЬгГЉгГЙпЉИLPB)зЫЄдЇТи®≠и®Ии¶Пж†ЉIEC 63055/IEEE2401-2019гБѓгАБгБУгВМгВТжЛЕгБЖгБЯгВБгБЃеЫљйЪЫж®ЩжЇЦгБІгБЩгАВеНКе∞ОдљУпЉЖгВЈгВєгГЖгГ†йЦЛзЩЇжКАи°УгВµгГЦгВ≥гГЯгГГгГЖгВ£гБѓгАБгБУгБЃж®ЩжЇЦгВТгГЩгГЉгВєгБЂгАМеНКе∞ОдљУгВТгВЈгВєгГЖгГ†и®≠и®ИгБЂзФЯгБЛгБЩгАНгАМгВЈгВєгГЖгГ†гБЃи¶Бж±ВгГїеИґзіДгВТеНКе∞ОдљУгБЂеПЦгВКиЊЉгВАгАНеПМжЦєеРСгБЃи®≠и®ИжКАи°УгБЃжХіеВЩгВТзЫЃжМЗгБЧз†Фз©ґгГїйЦЛзЩЇгВТи°МгБ£гБ¶гБДгБЊгБЩгАВгБУгБЃжіїеЛХгВТйАЪгБШгБ¶еНКе∞ОдљУзФ£ж•≠гБКгВИгБ≥йЫїе≠Рж©ЯеЩ®ж•≠зХМгБЃзЩЇе±ХгБЂеѓДдЄОгБЧгБ¶и°МгБНгБЊгБЩгАВ

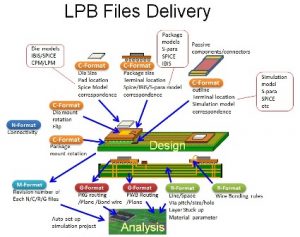

What is LPB ?

LPBгБ®гБѓLSIгГїгГСгГГгВ±гГЉгВЄгГїгГЬгГЉгГЙгБЃзЫЄдЇТи®≠и®ИгБЃгБУгБ®гБІгБЩгАВLPBгБМйА£жРЇгБЧеРИгБ£гБ¶зЂґдЇЙеКЫгБВгВЛи£љеУБи®≠и®ИгВТињЕйАЯгБЂдїХдЄКгБТгВЛгБУгБ®гВТзЫЃжМЗгБЧгБЊгБЩгАВ(more)>>

IEC 63055/IEEE2401-2019

LPBгБЂйЦҐгВПгВЛи®≠и®ИгБЂењЕи¶БгБ™жГЕ冱гВДи®≠и®ИзµРжЮЬгВТжµБйАЪгБХгБЫгВЛзВЇгБЂжИСгАЕгБМжО®йА≤гБЧгБ¶гБДгВЛеЫљйЪЫж®ЩжЇЦи¶Пж†ЉгБІгБЩпЉИи≥ЉеЕ•гБѓгБУгБ°гВЙгБЛгВЙпЉЙгАВгВµгГ≥гГЧгГЂгГХгВ°гВ§гГЂгБѓгАБгБУгБ°гВЙгБЛгВЙгГАгВ¶гГ≥гГ≠гГЉгГЙгБІгБНгБЊгБЩгАВ(more)>>

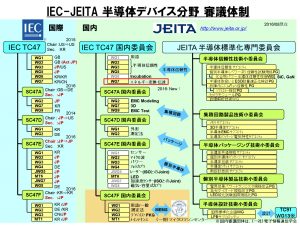

Organization

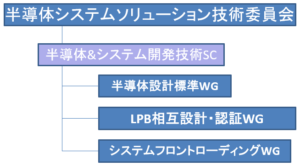

жИСгАЕгБЃзЫЃзЪДеЃЯзПЊгБЃзВЇгБЂгАБLPBйЦУгБЃи®≠и®ИгВ§гГ≥гВњгГЉгГХгВІгГЉгВєгБЃйЦЛзЩЇгАБгГҐгГЗгГЂгГЩгГЉгВєгГЗгВґгВ§гГ≥жКАи°УгБЃйЦЛзЩЇгАБгБЭгВМгВЙгВТеЫљйЪЫж®ЩжЇЦеМЦгБЩгВЛйГ®йЦАгВТи®≠зљЃгБЧгБ¶гБДгБЊгБЩгАВ(more)>>

еНКе∞ОдљУж®ЩжЇЦгГѓгГЉгВ≠гГ≥гВ∞гВ∞гГЂгГЉгГЧ

еНКе∞ОдљУж®ЩжЇЦгГѓгГЉгВ≠гГ≥гВ∞гВ∞гГЂгГЉгГЧгБѓгАБеЫљйЪЫж®ЩжЇЦи¶Пж†ЉгБЂдњВгВЛи®ИзФїгГїзЂЛж°ИгБ®гАБе∞ПеІФеУ°дЉЪгБЃгВєгГЖгВҐгГ™гГ≥гВ∞гВТи°МгБ£гБ¶гБДгБЊгБЩгАВ(more)>>

LPBзЫЄдЇТи®≠и®ИгГїи™Ни®ЉгГѓгГЉгВ≠гГ≥гВ∞гВ∞гГЂгГЉгГЧ

LPBзЫЄдЇТи®≠и®ИгГїи™Ни®ЉгГѓгГЉгВ≠гГ≥гВ∞гВ∞гГЂгГЉгГЧгБѓгАБIEC 63055/IEEE2401-2019гБЃйЦЛзЩЇгБ®жЩЃеПКгВТи°МгБ£гБ¶гБДгБЊгБЩгАВ(more)>>

гВЈгВєгГЖгГ†гГХгГ≠гГ≥гГИгГ≠гГЉгГЗгВ£гГ≥гВ∞гГѓгГЉгВ≠гГ≥гВ∞гВ∞гГЂгГЉгГЧ

гВЈгВєгГЖгГ†гГХгГ≠гГ≥гГИгГ≠гГЉгГЗгВ£гГ≥гВ∞гБѓLPBгБЂгБКгБСгВЛгВЈгГЯгГ•гГђгГЉгВЈгГІгГ≥гБКгВИгБ≥гГҐгГЗгГЂгГЩгГЉгВєгГЗгВґгВ§гГ≥жКАи°УгБЃз†Фз©ґйЦЛзЩЇгВТи°МгБ£гБ¶гБДгБЊгБЩгАВ (more)>>